Biestable

Un biestable o flip-flop (també anomenat bàscula), és un circuit electrònic multivibrador que pot romandre en un estat determinat o el contrari durant un temps indefinit fins que no rebi un impuls extern que l'obligui a canviar-lo, és a dir, no pot canviar per si mateix.[1] És a dir, pot emmagatzemar un bit de memòria. Quan parlem de flip-flop normalment ens referim a un dispositiu no-transparent (amb rellotge), mentre que un dispositiu transparent, més simple, seria un latch. El pas d'un estat a un altre es realitza variant les seves entrades.[2] Depenent del tipus d'entrades, els biestables es divideixen en:

- Asíncrons: només tenen entrades de control. El més emprat és el biestable RS.

- Síncrons: a més de les entrades de control, té una entrada de sincronisme o de rellotge. Si les entrades de control depenen de la de sincronisme, es denominen síncrones i en cas contrari asíncrones. En general, les entrades de control asíncrones prevalen sobre les síncrones.

Si les entrades de control depenen de la de sincronisme es denominen síncrones i en cas contrari asíncrones. En general, les entrades de control asíncrones prevalen sobre les síncrones.

L'entrada de sincronisme pot ser activada per nivell (alt o baix) o per flanc (de pujada o de baixada). Dins dels biestables síncrons activats per nivell estan els tipus RS i D, i dins dels actius per flancs els tipus JK, T i D.

Els biestables síncrons actius per flanc (flip-flop) es van crear per eliminar les deficiències dels latchs (biestables asíncrons o sincronitzats per nivell).

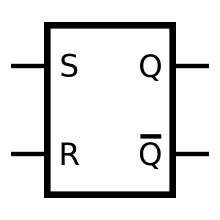

Biestable RS

[modifica]Descripció

Dispositiu d'emmagatzematge temporal de 2 estats (alt i baix), les entrades principals del qual permeten en ser activades:

- R: l'esborrat (reset en anglès), posada a 0 o nivell baix de la sortida.

- S: el gravat (set en anglès), posada a 1 o nivell alt de la sortida

Si no s'activa cap de les entrades, el biestable roman en l'estat que posseïa després de l'última operació d'esborrat o gravat. En cap cas haurien d'activar-se ambdues entrades alhora, ja que això provoca que les sortides directa (Q) i negada (Q') quedin amb el mateix valor: a baix, si el flip-flop està construït amb portes NOR, o alt, si està construït amb portes NAND. El problema que ambdues sortides quedin al mateix estat està en el fet que en desactivar ambdues entrades no es podrà determinar l'estat en el qual quedaria la sortida. Per això, en les taules de veritat, l'activació d'ambdues entrades es contempla com a cas no desitjat (N. D.).

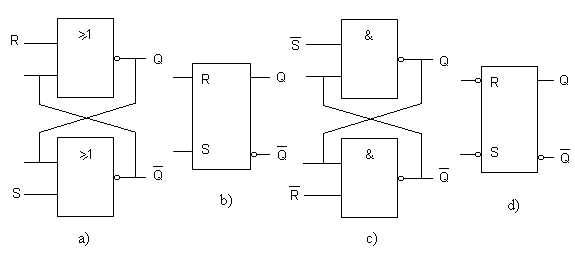

Biestable RS (Set Reset) asíncron

[modifica]Només posseeix les entrades R i S. Es compon internament de dues portes lògiques NAND o NOR, segons es mostra en la següent figura:

| R | S | Q (NOR) | Q (NAND) | ||||

|---|---|---|---|---|---|---|---|

0 |

0

|

q

|

N. D.

| ||||

0 |

1

|

1

|

0

| ||||

1 |

0

|

0

|

1

| ||||

1 |

1

|

N. D.

|

q

| ||||

| N. D.= Estat no desitjat q= Estat de memòria | |||||||

Biestable RS (Set Reset) síncron

[modifica]A més de les entrades R i S, posseeix una entrada C de sincronisme la missió del qual és la de permetre o no el canvi d'estat del biestable. En la següent figura es mostra un exemple d'un biestable síncron a partir d'una asíncrona, juntament amb el seu esquema normalitzat:

La seva taula de veritat és la següent:

| C | R | S | Q (NOR) |

|---|---|---|---|

0 |

X |

X

|

q

|

1 |

0 |

0

|

q

|

1 |

0 |

1

|

1

|

1 |

1 |

0

|

0

|

1 |

1 |

1

|

N. D.

|

| X=no importa | |||

Biestable D (Data o Delay)

[modifica]El flip-flop D resulta molt útil quan es necessita emmagatzemar un únic bit de dades (1 o 0). Si s'afegeix un inversor a un flip-flop S-R obtenim un flip-flop D bàsic. El funcionament d'un dispositiu activat pel flanc negatiu és, per descomptat, idèntic, excepte que el tret té lloc en el flanc de baixada del pols del rellotge. Recordi que Q segueix a D en cada flanc del pols de rellotge.

Per a això, el dispositiu d'emmagatzematge temporal és de dos estats (alt i baix), la sortida del qual adquireix el valor de l'entrada D quan s'activa l'entrada de sincronisme, C. En funció de la manera d'activació d'aquesta entrada de sincronisme, existeixen dos tipus:

- Actiu per nivell (alt o baix), també denominat registre o forrellat (latch en anglès).

- Actiu per flanc (de pujada o de baixada).

L'equació característica del biestable D que descriu el seu comportament és:

i la seva taula de veritat:

| D | Q | Qsegüent |

|---|---|---|

| 0 | X | 0

|

| 1 | X | 1

|

| X=no importa | ||

Aquesta bàscula pot veure's com una primitiva línia de retard o una retenció d'ordre zero (zero order hold en anglès), ja que les dades que s'introdueixen, s'obtenen en la sortida un cicle de rellotge després. Aquesta característica és aprofitada per sintetitzar funcions de processament digital de senyals (DSP en anglès) mitjançant la Transformada Z.

Exemple: 74LS74

Biestable T (Toggle)

[modifica]Dispositiu d'emmagatzematge temporal de 2 estats (alt i baix). El biestable T canvia d'estat («toggle» en anglès) cada vegada que l'entrada de sincronisme o de rellotge es dispara mentre l'entrada T està a nivell alt. Si l'entrada T està a nivell baix, el biestable reté el nivell previ. Pot obtenir-se en unir les entrades de control d'un biestable JK, unió que es correspon a l'entrada T.

L'equació característica del biestable T que descriu el seu comportament és:

i la taula de veritat:

| T | Q | Qsegüent |

|---|---|---|

| 0 | 0 | 0

|

| 0 | 1 | 1

|

| 1 | 0 | 1

|

| 1 | 1 | 0

|

Biestable JK

[modifica]És versàtil i és un dels tipus de flip-flop més usats. El seu funcionament és idèntic al del flip-flop S-R en les condicionis SET, RESET i de permanència d'estat. La diferència està que el flip-flop J-K no té condicions no vàlides com ocorre en el S-R.

Aquest dispositiu d'emmagatzematge és temporal que es troba dos estats (alt i baix), les entrades principals del qual, J i K, a les quals deu el nom, permeten en ser activades:

- J: El gravat (set en anglès), posada a 1 o nivell alt de la sortida.

- K: L'esborrat (reset en anglès), posada a 0 o nivell baix de la sortida.

Si no s'activa cap de les entrades, el biestable roman en l'estat que posseïa després de l'última operació d'esborrat o gravat. A diferència del biestable RS, en el cas d'activar-se ambdues entrades alhora, la sortida adquirirà l'estat contrari al que tenia.

L'equació característica del biestable JK que descriu el seu comportament és:

I la seva taula de veritat és:

| J | K | Q | Qsegüent |

|---|---|---|---|

| 0 | 0 | 0 | 0

|

| 0 | 0 | 1 | 1

|

| 0 | 1 | X | 0

|

| 1 | 0 | X | 1

|

| 1 | 1 | 0 | 1

|

| 1 | 1 | 1 | 0

|

| X=no importa | |||

Sent Q l'estat present i Qsegüent l'estat següent. L'equació característica del flip flop JK és: Qsegüent=JQ+KQ la qual s'obté de la taula característica del flip flop.

Una altra forma d'expressar la taula de veritat del biestable JK és mitjançant la denominada taula d'excitació:

| J | K | Q | Qsegüent |

|---|---|---|---|

| 0 | X | 0 | 0

|

| 1 | X | 0 | 1

|

| X | 1 | 1 | 0

|

| X | 0 | 1 | 1

|

| X=no importa | |||

Una forma més compacta de la taula de veritat és (Q representa l'estat següent de la sortida en el proper flanc de rellotge i q l'estat actual):

| J | K | Q |

|---|---|---|

| 0 | 0 | q |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

Biestable JK actiu per flanc

[modifica]Juntament amb les entrades J i K existeix una entrada C de sincronisme o de rellotge la missió del qual és la de permetre el canvi d'estat del biestable quan es produeix un flanc de pujada o de baixada, segons sigui el seu disseny. La seva denominació en anglès és J-K Flip-Flop Edge-Triggered. D'acord amb la taula de veritat, quan les entrades J i K estan a nivell lògic 1, a cada flanc actiu en l'entrada de rellotge, la sortida del biestable canvia d'estat. A aquesta manera de funcionament se li denomina manera de basculación (toggle en anglès).

Exemple: 74LS73

Biestable JK Mestre-Esclau

[modifica]Si bé encara pot trobar-se en alguns equips, aquest tipus de biestable, denominat en anglès J-K Flip-Flop Master-Slave, ha quedat obsolet, ja que ha estat reemplaçat pel tipus anterior.

El seu funcionament és similar al JK actiu per flanc: en el nivell alt (o baix) es prenen els valors de les entrades J i K i en el flanc de baixada (o de pujada) es reflecteix en la sortida.

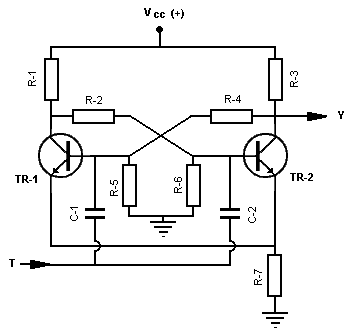

Exemple amb components discrets

[modifica]Encara que, en general, els biestables utilitzats en la pràctica estan implementats en forma de circuits integrats, en la Figura 1 es representa l'esquema d'un senzill circuit multivibrador biestable, realitzat amb components discrets, el funcionament dels quals és el següent:

En aplicar la tensió d'alimentació (Vcc), els dos transistors iniciaran la conducció, ja que les seves bases reben un potencial positiu, TR-1 a través del divisor format per R-3, R-4 i R-5 i TR-2 a través del format per R-1, R-2 i R-6, però com els transistors no seran exactament idèntics, pel mateix procés de fabricació i el grau d'impureses del material semiconductor, un conduirà abans o més ràpid que l'altre.

Suposem que és TR-1 el que condueix primer. El voltatge en el seu col·lector disminuirà, a causa de la major caiguda de tensió en R-1, per la qual cosa la tensió aplicada a la base de TR-2 a través del divisor format per R-2, R-6, disminuirà fent que aquest condueixi menys. Aquesta disminució de conducció de TR-2 fa que pugi la seva tensió de col·lector i, per tant, la de base de TR-1, aquest procés portarà finalment al bloqueig de TR-2 (sortida I a nivell alt).

Però si ara apliquem un impuls de tret de nivell alt per l'entrada T, a través dels condensadors C-1 i C-2 passarà a les bases de tots dos transistors. En el cas de TR-1 no tindrà més efecte que augmentar la seva tensió positiva, per la qual cosa est seguirà conduint. A la base de TR-2 l'impuls farà que aquest transistor condueixi, realitzant-se un procés similar al descrit al principi, quan el que conduïa primer era TR-1, que acabarà bloquejant a est i deixant en conducció a TR-2 (sortida I a nivell baix).

La seqüència descrita es repetirà cada vegada que s'apliqui un impuls en T. La sortida canvia d'estat amb l'impuls de tret i roman en aquest estat fins a l'arribada del següent impuls, moment en què tornarà a canviar.

La caiguda de tensió en la resistència comuna d'emissors (R-7) elimina la indecisió del circuit i augmenta la velocitat de commutació.

Aplicació

[modifica]Un biestable pot usar-se per emmagatzemar un bit. La informació continguda en molts biestables pot representar l'estat d'un seqüenciador, el valor d'un comptador, un caràcter ASCII en la memòria d'un ordinador, o qualsevol altra classe d'informació.

Un ús corrent és el disseny de màquines d'estat finites electròniques. Els biestables emmagatzemen l'estat previ de la màquina que s'usa per calcular el següent.

El T és útil per explicar. Un senyal repetitiu en l'entrada de rellotge fa que el biestable canviï d'estat per cada transició alt-baix si la seva entrada T està a nivell 1. La sortida d'un biestable pot connectar-se a l'entrada de rellotge de la següent i així successivament. La sortida final del conjunt considerat com una cadena de sortides de tots els biestables és el comptador en codi binari del nombre de cicles en la primera entrada de rellotge fins a un màxim de 2n-1, on n és el nombre de biestables usats.

Un dels problemes amb aquesta configuració de comptador (ripple counter en anglès) és que la sortida és momentàniament invàlida mentre els canvis es propaguen per la cadena just després d'un flanc de rellotge. Hi ha dues solucions a aquest problema. La primera, és mostrar la sortida només quan se sap que és vàlida. La segona, més complexa i àmpliament usada, és utilitzar un tipus diferent de comptador síncron, que té una lògica més complexa per assegurar que totes les sortides canvien al mateix moment predeterminat, encara que el preu a pagar és la reducció de la freqüència màxima a la qual pot funcionar.

Una cadena de biestables T com la descrita anteriorment també serveix per a la divisió de la freqüència d'entrada entre 2n, on n és el nombre de biestables entre l'entrada i l'última sortida.

Seqüenciació i metaestabilitat

[modifica]Els biestables síncrons són propensos a sofrir un problema denominat metaestabilitat, que ocorre quan una entrada de dades o de control està canviant al moment en el qual arriba un flanc de rellotge. El resultat és que la sortida pot comportar-se de forma imprevista, trigant moltes vegades més del normal a estabilitzar-se a l'estat correcte, o fins i tot podria oscil·lar repetides vegades fins a acabar en el seu estat estable. En un ordinador això pot suposar la corrupció de dades o causar una fallada de programa.

En molts casos, la metaestabilitat en els biestables es pot evitar assegurant-se que les dades i les entrades de control es mantenen constants durant un període especificat abans i després del flanc de rellotge, denominats setup time (tla seva) i hold time (th) respectivament. Aquests temps estan establerts en la fulla de dades del dispositiu en qüestió, i són típicament entre uns pocs nanosegons i uns pocs centenars de picosegons per a dispositius moderns.

Desafortunadament, no sempre és possible complir aquests requisits, perquè els biestables poden estar connectats a entrades en temps real que són asíncrones, i poden canviar a qualsevol moment fos del control del dissenyador. En aquest cas, l'única cosa que pot fer-se és reduir la probabilitat d'error a un determinat nivell, depenent de la fiabilitat que es desitgi del circuit. Una tècnica per reduir la incidència és connectar dues o més biestables en cadena, de manera que la sortida d'una es connecta a l'entrada de la següent, i amb tots els dispositius compartint el mateix senyal de rellotge. D'aquesta forma la probabilitat d'un succés metaestable pot reduir-se considerablement, però mai podrà eliminar-se per complet.

Existeixen biestables robusts enfront de la metaestabilitat, que funcionen reduint els temps de setup i hold en tot el possible, però fins i tot aquests no poden eliminar per complet el problema. Això és a causa que la metaestabilitat és molt més que un problema de disseny. Quan el flanc de rellotge i l'entrada de dades estan suficientment junts, el biestable ha de triar l'esdeveniment que va ocórrer abans. I per més ràpid que es faci el dispositiu, sempre existeix la possibilitat que succeeixin prou junts com perquè no es pugui detectar com és el que va ocórrer primer. Així doncs, és lògicament impossible el construir un biestable a prova de metaestabilitat.

Un altre paràmetre temporal important d'un biestable és el retard rellotge-a-sortida (clock-to-output tCO) o retard de propagació (propagation delay tP), que és el temps que el biestable triga a canviar la seva sortida després d'un flanc de rellotge. El temps per a una transició alt-a-baix (tPHL) és de vegades diferent del de les transicions de baix-a-alt (tPLH).

Quan es connecten biestables en cadena, és important assegurar que el tCO del primer és major que el hold time (tH) del següent, ja que en cas contrari, el segon biestable no rebrà les dades de forma fiable. La relació entre tCO i tH està garantida normalment si tots dos biestables són del mateix tipus.

Referències

[modifica]- ↑ «Bistable Multivibrator or Flip-flop Multivibrator» (en anglès), 05-09-2013. [Consulta: 27 agost 2021].

- ↑ Steven H. Strogatz. Nonlinear Dynamics and Chaos. Westview Press, 2001. ISBN 9780738204536.