DRAM

La Dynamic Random Access Memory (DRAM) és una memòria electrònica d'accés aleatori, que es fa servir principalment en els mòduls de memòria RAM i en altres dispositius, com a memòria principal del sistema. Es denomina dinàmica, ja que per a mantenir emmagatzemat una dada, es requereix revisar el mateix i recarregar-lo, cada cert període, en un cicle de refresc. El seu principal avantatge és la possibilitat de construir memòries amb una gran densitat de posicions i que encara funcionin a una velocitat alta: en l'actualitat es fabriquen integrats amb milions de posicions i velocitats d'accés amidats en milions de bit per segon. És una memòria volàtil, és a dir quan no hi ha alimentació elèctrica, la memòria perd la informació que tenia emmagatzemada. Inventada a la fi dels anys seixanta, és una de les memòries més utilitzades en l'actualitat.[1]

es fa servir principalment com a mòduls de memòria principal d'ordinadors i altres dispositius. El seu principal avantatge és la possibilitat de construir memòries amb una gran densitat de posicions i que encara funcionin a una velocitat alta: actualment es fabriquen integrats amb milions de posicions i velocitats d'accés mesurats en milions de bits per segon.

Com la resta de tipus de RAM, és volàtil de manera que si s'interromp l'alimentació elèctrica la informació emmagatzemada es perd. Va ser inventada a finals dels seixanta i és una de les memòries més usades actualment.[1] DRAM va tenir un augment del 47% en el preu per bit el 2017, el salt més gran en 30 anys des del salt del 45% el 1988, mentre que en els darrers anys el preu ha estat baixant.[2]

Història

[modifica]

La memòria dinàmica va ser desenvolupada als laboratoris d'IBM passant per un procés evolutiu que la va portar a fer servir 6 transistors a només un condensador i un transistor, com la memòria DRAM que coneixem avui. La invenció d'aquesta darrera la va fer Robert Dennard[3] qui va obtenir una patent nord-americana el 1968[4] per una memòria fabricada amb un sol transistor d'efecte de camp i un condensador.

IBM estava encaminat a millorar els seus equips de còmput, com per exemple la línia System 360: el model 25 el 1968 ja incloïa un ScratchPad (una mena de memòria cau controlada per programari) en forma d'integrats 5 vegades més ràpids que la memòria principal basada en nuclis de ferrita.[5] Donat el model de negocis d'IBM que consistia a vendre o arrendar ordinadors,[6] un negoci rendible, per a IBM lús de DRAM es reduïa a ser el complement de la memòria principal basada en nuclis magnètics. No hi va haver interès a comercialitzar aquest tipus de memòries per a altres fabricants ni tampoc es va pensar a usar les tecnologies d'estat sòlid tipus SRAM o DRAM per construir la memòria principal. L'empresa Intel va ser creada per aprofitar aquesta oportunitat de negocis: Gordon Moore, observava que fa temps la indústria dels semiconductors s'havia estancat, malgrat existir potencials usos dels integrats de silici com la fabricació de SRAM i DRAM.[7]

Encara que Intel es va iniciar amb SRAM com la i1101 i la i3101, el primer producte rendible va ser l'integrat de DRAM i1103 de 1024 bits. L'i1103 llançat el 1970 estava format per cel·les de memòria amb 3 transistors tipus PMOS i un condensador,[8] estava organitzat en un arranjament de 32 files i 32 columnes, empacat en un encapsulat de 18 pins i amb un cost d'1 cèntim per bit era un fort competidor per a les memòries de nucli. La producció i qualitat de l'integrat era difícil de mantenir, fet que es va demostrar quan Intel va lliurar part de la producció a una altra empresa anomenada Microelectronics Integrated Limited (MIL) que al principi va poder obtenir millors resultats que la mateixa Intel, però després del canvi important en el procés de fabricació no va ser capaç de produir.[7]

La memòria i1103 era molt primitiva en comparació a les DRAM de l'actualitat, tot i així es comportava millor que la memòria de nucli i amb un preu menor. A finals de 1971 s'havia convertit en el producte dominant per a la fabricació de memòria principal i era usat per 14 entre 18 dels principals fabricants d'ordinadors,[9] guanyant el malnom "core killer".[10]

Reinvenció de la memòria DRAM

[modifica]Vora l'any 1973 Intel i altres fabricants construïen els seus integrats de memòria DRAM emprant un esquema en el qual s'augmentava un pin cada vegada que es doblava la capacitat. D'acord amb aquest esquema, un integrat de 64 kbits tindria 16 pins només per a les adreces. Dintre dels costos més importants pel fabricant i l'ensamblador de circuits impresos estava la quantitat de pins de l'empaquetatge i en un mercat tan competit era crucial tenir els menors preus. A causa d'això, un integrat amb una capacitat de 16 pins i 4Kb de capacitat va ser un producte d'èxit pels usuaris, que trobaven als integrats de 22 pins, oferts per Intel i Texas Instruments menys costosos.

El llançament de la memòria MK4096 de 4K, amb un sol transistor per cel·la i amb adreçament multiplexat sorgit del treball de Robert Proebsting qui observà que en les cel·les amb un sol transistor, era impossible accedir a la informació en una posició, enviant al mateix temps les dades de fila i columna a la matriu: calia doncs enviar els senyals un després de l'altra. La solució a nivell de la cel·la conduïa a un estalvi en l'empaquetatge, ja que l'adreça podria rebre's en dues etapes, reduint la quantitat de pins usats. Per exemple per a un integrat de 64 Kb es passava de 16 pins dedicats a solament 8 i dos mes per a senyals de control extres. La multiplexació en el temps és un esquema d'adreçament que porta molts avantatges, a costa d'uns pocs canvis en el circuit extern, de manera que va esdevenir un estàndard de la indústria que encara es manté. Molta de la terminologia usada en la fulla de dades del MK4096 encara es fa servir i molts dels paràmetres de temporització com el retard RAS a CAS van ser instaurats amb aquest producte, entre altres aspectes.[11]

Funcionament

[modifica]La cel·la de memòria és a la unitat bàsica de qualsevol memòria, capaç d'emmagatzemar un Bit en els sistemes digitals. La construcció de la cel·la defineix el funcionament d'aquesta, en el cas de la DRAM moderna, consisteix en un transistor d'efecte de camp i un condensador. El principi de funcionament bàsic, és senzill: una càrrega s'emmagatzema en el condensador significant un 1 i sense càrrega un 0. El transistor funciona com un interruptor que connecta i desconnecta al condensador. Aquest mecanisme pot implementar-se amb dispositius discrets i de fet moltes memòries anteriors a l'època dels semiconductors, es basaven en arranjaments de cel·les transistor-condensador.

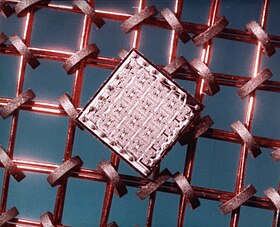

Les cel·les en qualsevol sistema de memòria, s'organitzen en la forma de matrius de dues dimensions, a les quals s'accedeix per mitjà de les files i les columnes. En la DRAM aquestes estructures contenen milions de cel·les i es fabriquen sobre la superfície de la pastilla de silici formant àrees que són visibles a primera vista. Normalment les memòries DRAM s'agrupen en els anomenats DIMMs (Dual Inline Memory Modules) que poden contenir diversos xips DRAM i que comuniquen els diferents xips amb els busos de memòria.

En l'exemple tenim un arranjament de 4x4 cel·les, en el qual les línies horitzontals connectades a les comportes dels transistors són les files i les línies verticals connectades als canals dels FET són les columnes.

Per a accedir a una posició de memòria es necessita una adreça de 4 bits, però en les DRAM les adreces estan multiplexades en temps, és a dir s'envien a parts iguals. Les entrades marcades com a0 i a1 són el bus d'adreces i pel mateix entra la direcció de la fila i després la de la columna. Les adreces es diferencien per mitjà de senyals de sincronització anomenats RAS (de l'anglès Row Address Strobe) i CAS (Column Address Strobe) que indiquen l'entrada de cada part de l'adreça.

la latència CAS és el temps de retard que transcorre entre el moment en què un controlador de memòria demana al mòdul de memòria d'accedir a una columna en particular de la memòria en un mòdul de memòria DRAM, i el moment en què les dades demanades són disponibles als pins de sortida del mòdul.[12]

Passos principals per a una lectura

[modifica]- Les columnes són precarregades a un voltatge igual a la meitat del voltatge d'1 lògic. Això és possible, ja que les línies es comporten com grans condensadors, donada la seva longitud tenen un valor més alt que la dels condensadors en les cel·les.

- Una fila és energitzada per mitjà del descodificador de files que rep la direcció i el senyal de RAS. Això fa que els transistors connectats a una fila condueixin permetent la connexió elèctrica entre les línies de la columna i una fila de condensadors. L'efecte és el mateix que es produeix al connectar dos condensadors, uneixo carregat i altre de càrrega desconeguda: es produeix un balanç que deixa als dos amb un voltatge molt similar, compartint les càrregues. El resultat final depèn del valor de càrrega en el condensador de la cel·la connectada a cada columna. El canvi és petit, ja que la línia de columna és un condensador més gran que el de la cel·la.

- El canvi és amidat i amplificat per una secció que conté circuits de realimentació positiva: si el valor a amidar és menor que el de la meitat del voltatge d'1 lògic, la sortida serà un 0, si és major, la sortida es regenera a un 1. Funciona com un arrodoniment.

- La lectura es realitza en totes les posicions d'una fila de manera que en arribar la segona part de l'adreça, es decideix com és la cel·la desitjada. Això succeeix amb el senyal CAS. La dada és lliurada al bus de dades per mitjà de la línia D.O. i les cel·les involucrades en el procés són reescrites, ja que la lectura de la DRAM és destructiva.

L'escriptura en una posició de memòria té un procés similar al de dalt, però en comptes de llegir el valor, la línia de columna es duu a un valor indicat per la línia D.I. i el condensador és carregat o descarregat. El flux de la dada és mostrat amb una línia gruixuda en el gràfic.

Evolució de la memòria DRAM

[modifica]Les memòries DRAM han anat evolucionant amb la millora de la integració dels xips i s'espera que en poc temps arribi als 4 Gb (Giga bits) de capacitat de memòria per xip. L'altra cosa que l'ha anat fent millorar és la reducció del voltatge dels chips que han anat passant dels 5 Volts als 1,8 Volts de l'actualitat cosa que ha fet baixar el consum.

Les primeres DRAM que van aparèixer eren asíncrones, és a dir, que els seus busos no tenien la mateixa freqüència de rellotge o un múltiple d'ella que la freqüència de rellotge de la CPU que les utilitzava, això provocava que les esperes o latències per fer-la servir eren més elevades que si foren asíncrones, ja que les esperes es devien al fet que s'havien de sincronitzar, ja que no ho estaven.

Per millorar les esperes primer es va desenvolupar el que s'anomena burst mode access que permetia fer com una mena de prefetching amb les dades que s'havien de posar al bus per tal de reduir els cicles de rellotge d'un accés.

Amb aquest mètode que en cada seqüència de CAS i RAS es porten quatre vegades més de dades i es redueixen els temps d'espera, ja que es realitzen menys CAS que als sistemes inicials en els quals per cada bloc de 64 bits s'havien de fer un CAS i un RAS.

Això intentava contrarestar el fet de les esperes per l'asincronia, però ben aviat es va passar a desenvolupar la DRAM de manera que fos sincrònica amb el rellotge de la CPU, apareixien les SDRAM.

Disseny de cel·les de memòria

[modifica]Cada bit de dades en una DRAM s'emmagatzema com a càrrega elèctrica positiva o negativa en una estructura capacitiva. L'estructura que proporciona la capacitància, així com els transistors que controlen l'accés a aquesta, es denominen col·lectivament "cel·la DRAM". Són el bloc de construcció fonamental a les matrius DRAM. Hi ha múltiples variants de cel·les de memòria DRAM, però la variant més utilitzada a les DRAM modernes és la cel·la d'un transistor, un capacitor (1T1C). El transistor s'utilitza per admetre corrent al condensador durant les escriptures i per descarregar el condensador durant les lectures. El transistor d'accés està dissenyat per maximitzar la potència de la unitat i minimitzar les fuites de transistor a transistor (Kenner, pág. 34).

El condensador té dos terminals, un dels quals està connectat al transistor d'accés i l'altre a terra o VCC/2. A les DRAM modernes, aquest últim cas és més comú, ja que permet un funcionament més ràpid. A les DRAM modernes, un voltatge de +VCC/2 a través del condensador es requereix emmagatzemar-ne un de lògic; i un voltatge de -VCC/2 a través del condensador es requereix per emmagatzemar un zero lògic. La càrrega elèctrica emmagatzemada al condensador es mesura en colombi. Per a una lògica, el càrrec és: , on Q és la càrrega en coulombs i C és la capacitància en faradis. Un zero lògic té una càrrega de: .[13]

Llegir o escriure una lògica requereix que la línia de paraules es condueixi a un voltatge més gran que la suma de VCC i el voltatge de llindar del transistor d'accés (VTH). Aquest voltatge es diu VCC bombejat (VCCP). El temps requerit per descarregar un condensador depèn de quin valor lògic s'emmagatzema al condensador. Un condensador que conté un lògic comença a descarregar quan el voltatge a la terminal de porta del transistor daccés està per sobre de VCCP. Si el condensador conté un zero lògic, es comença a descarregar quan el voltatge del terminal de la porta està per sobre VTH.[14]

Vegeu també

[modifica]- nano-RAM: RAM amb nanotubs de carboni.

- SRAM: RAM estàtica.

- Flaix: memòria flaix.

- E2PROM: memòria esborrable elèctricament.

- ReRAM: memòria RAM resistiva.

- FeRAM: memòria ferromagnètica.

- MRAM: memòria RAM magnetorresistiva

Referències

[modifica]- ↑ 1,0 1,1 «What is DRAM (dynamic random access memory)? - Definition from WhatIs.com» (en anglès). SearchStorage.

- ↑ «Are the Major DRAM Suppliers Stunting DRAM Demand?». www.icinsights.com. Arxivat de l'original el 2018-04-16. [Consulta: 16 abril 2018].

- ↑ http://www.research.ibm.com/journal/rd/391/adler.html Arxivat 2008-05-02 a Wayback Machine. Història d'investigacions d'IBM (en anglès)

- ↑ http://www.freepatentsonline.com/3387286.pdf Patente # 3'387.286 para la memoria DRAM

- ↑ http://www-03.ibm.com/ibm/history/exhibits/mainframe/mainframe_PP2025.html Descripció de l'equip System 360 model 25 d'IBM

- ↑ «IBM Archives: System/370 Model 195». [Consulta: 2009].

- ↑ 7,0 7,1 The Power of Boldness: "Ten Master Builders of American Industry Tell Their Success Stories" página 82

- ↑ «DRAM - A Personal View». [Consulta: 2009].

- ↑ «Museum».

- ↑ «EETimes.com». [Consulta: 2009].

- ↑ «Dynamic RAM Tutorial | DRAM Memory Technology | Radio-Electronics.Com» (en anglès). [Consulta: 23 gener 2017].

- ↑ «What is the difference between static RAM and dynamic RAM?» (en anglès). HowStuffWorks, 24-08-2000.

- ↑ Keeth et al. 2007, p. 22

- ↑ Keeth et al. 2007, p. 24

Bibliografia

[modifica]- Keeth, Brent; Baker, R. Jacob; Johnson, Brian; Lin, Feng. Wiley. DRAM Circuit Design: Fundamental and High-Speed Topics, 2007. ISBN 978-0470184752.

- Jacob, Bruce; Wang, David; Ng, Spencer. Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann, 2010. ISBN 978-0-08-055384-9.