Multiplexor i demultiplexor

| Aquest article tracta sobre un dispositiu selector de senyals. Per a telecomunicacions, vegeu multiplexació |

En electrònica, un multiplexor (o MUX, també anomenat multiplexador), també conegut com a selector de dades, és un dispositiu que selecciona entre diversos senyals d'entrada analògics o digitals i reenvia l'entrada seleccionada a una única línia de sortida.[1] La selecció està dirigida per un conjunt separat d'entrades digitals conegudes com a línies de selecció o senyal de control. Un multiplexor de entrades té línies de selecció, que s'utilitzen per seleccionar quina línia d'entrada ha d'enviar a la sortida.[2]

Un multiplexor fa possible que diversos senyals d'entrada comparteixin un dispositiu o recurs, per exemple, un convertidor analògic-digital o un mitjà de transmissió de comunicacions, en lloc de tenir un dispositiu per senyal d'entrada. Els multiplexors també es poden utilitzar per implementar funcions booleanes de múltiples variables.

-

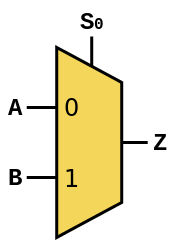

Esquema d'un multiplexor 2 a 1. Es pot equiparar a un interruptor controlat

L'esquema superior mostra un multiplexor 2 a 1 a l'esquerra i un interruptor equivalent a la dreta. El cable connecta l'entrada desitjada a la sortida.

Per contra, un demultiplexor (o DEMUX) és un dispositiu que pren una única entrada i selecciona els senyals de sortida del mux compatible, que està connectat a l'entrada única, i una línia de selecció compartida. Sovint s'utilitza un multiplexor amb un demultiplexor complementari a l'extrem receptor.[1]

-

Esquema d'un demultiplexor 1 a 2. Com un multiplexor, es pot equiparar a un interruptor controlat

Un multiplexor electrònic es pot considerar com un commutador d'entrada múltiple i sortida simple (MISO, Multiple Inputs, Single Output), i un demultiplexor com un interruptor d'entrada simple i sortida múltiple (SIMO, Single Input, Multiple Outputs).[3] El símbol esquemàtic d'un multiplexor és un trapezi isòsceles amb el costat paral·lel més llarg que conté els pins d'entrada i el costat paral·lel curt conté el pin de sortida.[4]

Aplicacions

[modifica]Els multiplexors formen part dels sistemes informàtics per seleccionar dades d'una font específica, ja sigui un xip de memòria o un perifèric de maquinari. Un ordinador utilitza multiplexors per controlar els busos de dades i direccions, permetent al processador seleccionar dades de múltiples fonts de dades.

-

La funció bàsica d'un multiplexor és combinar múltiples entrades en un sol flux de dades. Al costat receptor, un demultiplexor divideix el flux de dades únic en els múltiples senyals originals.

En les comunicacions digitals, els multiplexors permeten diverses connexions a través d'un sol canal, connectant la sortida única del multiplexor a l'entrada única del demultiplexor (multiplexació per divisió temporal). La imatge superior demostra aquest benefici. En aquest cas, el cost d'implementar canals separats per a cada font de dades és superior al cost i inconvenient de proporcionar les funcions de multiplexació/demultiplexació.

A l'extrem receptor de l'enllaç de dades, normalment es requereix un demultiplexor complementari per trencar el flux de dades únic en els fluxos originals. En alguns casos, el sistema de l'extrem llunyà pot tenir una funcionalitat més gran que un simple demultiplexor; i tot i que la demultiplexació encara es produeix tècnicament, és possible que mai s'implementa de manera discreta. Aquest seria el cas quan, per exemple, un multiplexor dona servei a diversos usuaris de la xarxa IP; i després s'alimenta directament a un encaminador, que llegeix immediatament el contingut de tot l'enllaç al seu processador d'encaminament; i després fa la demultiplexació a la memòria des d'on es convertirà directament en seccions IP.

Sovint, un multiplexor i un demultiplexor es combinen en un únic equip, que simplement es coneix com a multiplexor. Els dos elements del circuit són necessaris als dos extrems d'un enllaç de transmissió perquè la majoria dels sistemes de comunicacions transmeten en ambdues direccions (duplex).

En el disseny de circuits analògics, un multiplexor és un tipus especial d'interruptor analògic que connecta un senyal seleccionat entre diverses entrades a una única sortida.

Multiplexors digitals

[modifica]En el disseny de circuits digitals, els cables de selecció són de valor digital. En el cas d'un multiplexor 2 a 1, un valor lògic de 0 connectaria a la sortida, mentre que un valor lògic d'1 connectaria a la sortida. En multiplexors més grans, el nombre de pins de selecció és igual a on és el nombre d'entrades. Per exemple, de 9 a 16 entrades requeririen no menys de 4 pins de selecció i de 17 a 32 entrades requeririen no menys de 5 pins de selecció. El valor binari expressat en aquests pins selectors determina el pin d'entrada seleccionat.

Un multiplexor 2 a 1 té una equació booleana on i són dues entrades, és l'entrada del selector és la sortida:

que es pot expressar com una taula de veritat:

| (selector) | (entrada) | (entrada) | (sortida) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

O, en notació més senzilla

| 0 | A |

| 1 | B |

Aquestes taules mostren que quan aleshores , però quan aleshores . Una realització senzilla d'aquest multiplexor 2 a 1 necessitaria 2 portes AND, una porta OR i una porta NOT. Tot i que això és matemàticament correcte, una implementació física directa seria propensa a situacions de competició que requereixen portes addicionals per suprimir.[5]

-

Estructura d'un multiplexor amb una porta NOT, dues AND (&) i una porta OR (≥1)

-

Símbol d'un multiplexor segons DIN 40900; la imatge defineix l'estructura interna (G = AND; V = OR; 1 = identitat; 1 = negació)

Els multiplexors més grans també són habituals i, com s'ha dit anteriorment, requereixen pins de selecció per entrades. Altres mides habituals són 4 a 1, 8 a 1 i 16 a 1. Com que la lògica digital utilitza valors binaris, s'utilitzen potències de 2 (4, 8, 16) per controlar al màxim un nombre d'entrades per al nombre donat d'entrades de selecció.

-

Multiplexor 4 a 1

-

Multiplexor 8 a 1

-

Multiplexor 16 a 1

L'equació booleana per a un multiplexor 4 a 1 és:

-

Multiplexor 4 a 1 que utilitza quatre portes AND, dues NOT i tres OR

El següent multiplexor 4 a 1 es construeix a partir de lògica de 3 estats i portes AND (les portes AND actuen com a descodificador):

-

Multiplexor 4 a 1 de lògica de tres estats

Els subíndexs a les entrades indiquen el valor decimal de les entrades de control binaris a les quals es deixa passar aquesta entrada.

Cadenes de multiplexors

[modifica]Els multiplexors més grans es poden construir utilitzant multiplexors més petits encadenant-los. Per exemple, un multiplexor de 8 a 1 es pot fer amb dos multiplexors de 4 a 1 i un de 2 a 1. Les dues línies de selecció dels multiplexors 4 a 1 són alimentades pel multiplexor 2 a 1, amb les línies de selecció dels multiplexors 4 a 1 posats en paral·lel, que equival a un multiplexor 8 a 1.

2-MUX

[modifica]La figura a mostra l'estructura recursiva d'un multiplexor doble (2-MUX per abreujar) a partir d'un multiplexor simple (1-MUX). De la mateixa manera, els multiplexors es poden construir amb encara més línies de selecció i, per tant, més entrades. Per a la construcció d'un m-MUX, es requereixen 2m-1 MUX amb m línies de selecció cadascun. Per tant, el nombre d'entrades i els costos d'un multiplexor augmenten exponencialment amb el nombre de les seves línies de selecció.

Els multiplexors amb moltes línies de selecció tenen un gran nombre de portes d'entrada, la qual cosa comporta un temps de propagació llarg.

| s0 | s1 | a |

|---|---|---|

| 0 | 0 | e0 |

| 0 | 1 | e₂ |

| 1 | 0 | e1 |

| 1 | 1 | e₃ |

-

Símbol del segons DIN 40900; l'etiquetatge descriu l'estructura interna

La funció booleana d'aquest 2-MUX és:

| s0 | s1 | a |

|---|---|---|

| 0 | 0 | e0 |

| 0 | 1 | e1 |

| 1 | 0 | e₂ |

| 1 | 1 | e₃ |

-

Símbol del circuit segons DIN 40900

-

Símbol del circuit amb notació de dependència simplificada

La funció booleana d'aquest 2-MUX és:

3-MUX

[modifica]Tanmateix, també és possible implementar la mateixa funció de selecció amb un 3-MUX. El problema és que la funció f té quatre paràmetres però només hi ha tres línies de selecció disponibles. Es resol expressant el valor de la funció a en termes de s₃.

Això produeix la següent taula de veritat:

| s₂ | s1 | s0 | a |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | S₃ |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | S₃ |

El 3-MUX es connecta de la següent manera:

-

Estructura pràctica d'un 3-MUX

-

Estructura pràctica d'un 3-MUX format per multiplexors individuals (variant 1)

-

Estructura pràctica d'un 3-MUX format per multiplexors individuals (variant 2)

4-MUX

[modifica]Es dona una funció de selecció f(s₃,s₂,s1,s0), que és 1 si i només si el nombre binari [s₃s₂s1s0]₂ és un nombre primer. Per exemple, f(0, 0, 1, 1) = 1, ja que el nombre binari 0011 correspon al decimal 3 i el 3 és un nombre primer (com que l'1 no és un nombre primer, la lògica de 0 0 0 1 a la sortida a seguida d'un 0).

La funció f correspon a la següent taula de veritat:

| Decimal | s₃ | s₂ | s1 | s0 | a |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 |

| 11 | 1 | 0 | 1 | 1 | 1 |

| 12 | 1 | 1 | 0 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 |

| 14 | 1 | 1 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 |

Aquesta funció de selecció s'ha d'implementar amb un 4-MUX. Els bits presents a les entrades del 4-MUX es poden llegir a la columna de resultats a de la taula de veritat. Per tant, el 4-MUX s'ha de canviar de la següent manera:

-

Estructura pràctica d'un 4-MUX

Llista de circuits integrats que proporcionen multiplexació

[modifica]Per als números de peça de la sèrie 7400 de la taula següent, «x» és la família lògica.

| IC No. | Funció | Estat de la sortida |

|---|---|---|

| 74x157 | mux quad 2:1 | La sortida és igual que l'entrada donada |

| 74x158 | mux quad 2:1 | La sortida és una entrada invertida |

| 74x153 | mux dual 4:1 | La sortida és igual que entrada |

| 74x352 | mux dual 4:1 | La sortida és una entrada invertida |

| 74x151A | mux 8:1 | Dues sortides disponibles (és a dir, sortides complementàries) |

| 74x151 | mux 8:1 | La sortida és una entrada invertida |

| 74x150 | mux 16:1 | La sortida és una entrada invertida |

Demultiplexors digitals

[modifica]Els demultiplexors tenen una entrada de dades, diverses línies de selecció, i tenen diverses sortides. Reenvien l'entrada de dades a una de les sortides en funció dels valors de les entrades de selecció. Els demultiplexors de vegades són convenients per dissenyar lògica de propòsit general perquè si l'entrada del demultiplexor sempre és certa, el demultiplexor actua com un descodificador binari. Això vol dir que amb qualsevol funció de bits de selecció es pot construir el conjunt correcte de sortides mitjançant portes lògiques OR.

Si X és l'entrada, S és el selector, i A i B són les sortides:

-

Exemple: un demultiplexor d'1 a 4 línies d'un sol bit

-

Esquema lògic d'un demultiplexor de 2 entrades i 4 sortides

Llista de circuits integrats que proporcionen demultiplexació

[modifica]Per als números de peça de la sèrie 7400 de la taula següent, «x» és la família lògica.

| IC No. (7400) | IC No. (4000) | Funció | Estat de la sortida |

|---|---|---|---|

| 74x139 | demux dual 1:4 | La sortida és una entrada invertida | |

| 74x156 | demux 1:4 | La sortida és un col·lector obert | |

| 74x138 | demux 1:8 | La sortida és una entrada invertida | |

| 74x238 | demux 1:8 | ||

| 74x154 | demux 1:16 | La sortida és una entrada invertida | |

| 74x159 | CD4514/15 | demux 1:16 | La sortida és de col·lector obert i igual que l'entrada |

Multiplexors com a PLD

[modifica]Els multiplexors també es poden utilitzar com a dispositius lògics programables (PLD), per implementar funcions booleanes. Qualsevol funció booleana de n variables i un resultat es pot implementar amb un multiplexor amb n línies de selecció. Les variables es connecten a les entrades de les línies de selecció i el resultat de la funció, 0 o 1, per a cada combinació possible d'entrades de les línies de selecció es connecta a l'entrada de dades corresponent.

Si una de les variables (per exemple, D) també està disponible invertida, n'hi ha prou amb un multiplexor amb n-1 línies de selecció; les entrades de dades estan connectades a 0, 1, D o D, segons la sortida desitjada per a cada combinació d'entrades de les línies de selecció.[6]

Referències

[modifica]- ↑ 1,0 1,1 Dean, 2010, p. 82-85.

- ↑ Debashis, 2010, p. 557.

- ↑ Lipták, 2002, p. 343.

- ↑ Harris, 2007, p. 79.

- ↑ Crowe i Barrie, 1998, p. 111-113.

- ↑ Lancaster, 1974, p. 140-143.

Bibliografia

[modifica]- Crowe, John; Hayes-Gill, Barrie. «The multiplexer hazard». A: Introduction to Digital Electronics (en anglès). Elsevier, 1998. ISBN 9780080534992.

- Dean, Tamara. Network+ Guide to Networks (en anglès). Delmar, 2010. ISBN 978-1423902454.

- Debashis, De. Basic Electronics (en anglès). Dorling Kindersley, 2010, p. 557. ISBN 9788131710685.

- Harris, David. Digital Design and Computer Architecture (en anglés). Penrose, 2007. ISBN 9780080547060.

- Lancaster, Donald E. The TTL Cookbook (en anglès). H. W. Sams, 1974. ISBN 9780672210358.

- Lipták, Béla. Instrument engineers' handbook: Process software and digital networks (en anglès). CRC Press, 2002. ISBN 9781439863442.

- Mano, M. Morris; Kime, Charles R. Logic and Computer Design Fundamentals (en anglès). Prentice Hall, 2008. ISBN 978-0-13-198926-9.

Vegeu també

[modifica]Enllaços externs

[modifica]- ACADENAS. «Multiplexores analogicos y digitales» (en castellà). YouTube.

- ACADENAS. «(Parte I) Aplicaciones y ampliaciones de los MUX analogicos y digitales» (en castellà). YouTube.

- ACADENAS. «(Parte II) Aplicaciones y ampliaciones de los MUX analogicos y digitales» (en castellà). YouTube.

- ACADENAS. «Todo sobre los decodificadores» (en castellà). YouTube.