SoC

System-on-a-chip o SoC (traduït seria sistema en un xip), descriu la tendència cada vegada més freqüent d'usar tecnologies de fabricació que integren tots o gran part dels mòduls components d'un ordinador o qualsevol altre sistema informàtic o electrònic en un únic circuit integrat o xip. El disseny d'aquests sistemes pot estar basat en circuits de senyal digital, senyal analògic, o fins i tot de senyal mixt (tant analògic com digital), i sovint mòduls o sistemes de radiofreqüència (mòduls de comunicació sense fils: Wi-Fi, Bluetooth, etc.). Un àmbit comú d'aplicació de la tecnologia SoC són els sistemes embeguts.

Les diferència principal d'un SoC amb un microcontrolador tradicional no ha de passar per alt, ja que aquests poques vegades disposen de més de 100 Kilobytes de memòria RAM (de fet, el més freqüent és que les memòries d'un microcontrolador només consti (n) d'uns pocs Kilobytes), i gran part d'aquests són estructures mono-xip, mentre que el terme SoC és usat per processadors més potents i complexos, com són els dels ordinadors actuals, i que depenen de xip sobre mòduls de memòria externs per ser eficaços.[1] Per a sistemes més grans i complexos seria impropi parlar de SoCs, convertint-se el terme, en aquest cas, en una mera referència o directiva seguir que la pròpia realitat d'aquests:

- Augmentar la integració en un mateix xip amb l'objectiu de reduir costos i construir sistemes cada vegada més reduïts (capaços del mateix o més que sistemes més antics i voluminosos).

Resultaria impropi, principalment, perquè els interessos de la majoria dels projectes desenvolupats en aquesta àrea fixen els seus objectius en dissenys tan específics i complexos que no solen permetre-a causa del cost d'aquests-la implementació de tot el sistema en un sol xip. Aquests solen ser dissenyats expressament per a una optimització en la realització d'un (o més) dels processos que suposen gran part de la rutina de funcionament.

Una alternativa al disseny i fabricació d'un SoC-quan això no sigui rendible, per exemple-per a una determinada aplicació és un sistema System-in-package (o SiP), que comprèn un nombre determinat de xips acoblats en un de sol. Tot i això, s'estima que la fabricació en gran volum de SoCs serà més rendible que la de sistemes SiP, pel fet que el rendiment de fabricació unitari per a un SoC és gran i el seu muntatge i empaquetat molt més senzills.[2]

Una tercera opció en la integració de sistemes electrònics, present per exemple en telèfons mòbils d'alta gamma, o el Board (un senzill ordinador de baixa potència basat en el processador OMAP de Texas Instruments), és l'apilament de diferents plaques de circuits en assemblar el sistema (package-on-package o POP). Consisteix, bàsicament, en la soldadura de la placa principal-la que conté el processador-amb plaques superiors i inferiors mitjançant un entramat d'esferes metàl·liques (BGA, ball grid array) en forma d'anell. Aquestes proporcionen consistència a l'estructura en forma de sandvitx alhora que interconnecten el processador (i altres components principals) amb els busos de memòria situada a una placa diferent apilades sota o sobre la principal. Normalment aquestes plaques són fabricades i distribuïdes per diferents empreses que les que dissenyen microcontroladors, microprocessadors i SoCs.[3]

Arquitectura

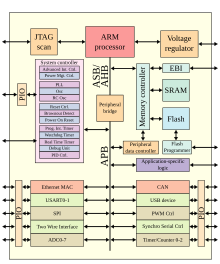

[modifica]Un SoC estàndard està constituït per:

- Un microcontrolador, microprocessador o nucli processador de senyals digitals. Alguns SoCs - anomenats MultiProcessor System-on-Chip (MPSoC) - són construïts amb microprocessadors dotats de diversos nuclis o bé més d'un microprocessador.

- Mòduls de memòria incloent part o tots els tipus de memòria a continuació llistats: ROM (memòria de només lectura), RAM (memòria d'accés aleatori), EEPROM (memòria de només lectura programable i esborrable electrònicament) i Flash (memòries NAND d'accés molt ràpid en comparació amb els tradicionals-encara avui molt usats-suports magnètics).

- Generadors de freqüència fixa com ara oscil·lador si/o llaços de seguiment de fase o PLLs.

- Components perifèrics com comptadors-temporitzadors, temporitzador sobre rellotges a temps real i generadors PEL (power-on reset, dispositius que reajusten el sistema en rebre senyal positiu, permetent a un sistema electrònic arrencar des d'un estat conegut).

- Interfícies externes incloent estàndards com USB, IEEE 1394/Firewire, Ethernet, USART, o SPI.

- Interfícies analògiques incloent ADCS i DACs.

- Reguladors de voltatge i circuits de power management.

Aquests mòduls estan interconnectats d'acord amb estàndards industrials de connexió de busos com també a tecnologies propietàries com ara l'especificació AMBA, arquitectura de bus dissenyada per ARM Ltd. Controladors DMA dedicats dirigeixen la informació entre interfícies externes i la memòria principal, evitant el pas innecessari d'aquesta a través del processador i incrementant així el volum de treball del SoC.

Procés de disseny

[modifica]Un SoC està constituït, d'una banda, pel maquinari amunt descrit, i per una altra del programari que gestiona els (o els) nucli (s) del microcontrolador, processador, o processador de senyals digitals, a més dels perifèrics i ports o interfícies. Una bona planificació del disseny d'un SoC tractarà de desenvolupar paral·lelament l'arquitectura física o maquinari i el programari.

La majoria de SoCs són desenvolupats a partir de mòduls de maquinari bàsics prèviament testejats per a la construcció de diversos elements (llistats anteriorment) més complexos juntament amb els controladors de programari que proporcionen les instruccions per al seu maneig. De gran importància són les famílies de protocols d'Internet que manegen interfícies universals com el famós universal serial bus (USB). Els mòduls de maquinari es posicionen sobre les plaques de la manera més òptima (compactant en l'espai disponible la major quantitat possible de components) amb ajuda d'eines CAD, permetent elaborar un disseny previ de l'arquitectura que es desitja fabricar sense cost addicional. Al seu torn, els mòduls de programari s'implementen en el sistema final usant potents eines de desenvolupament, conegudes com a IDE i SDE.

Un pas clau en la confecció del SoC és l'emulació: el maquinari es mapa tal com serà fabricat en una plataforma d'emulació basada en un FPGA, que reprodueix fidelment el comportament del SoC, per tal de testejar els mòduls de programari. Per això, aquests són carregats a la memòria volàtil de l'emulador. Un cop posada a punt, la plataforma és posada en funcionament: tant el maquinari com el programari rèpliques del futur SoC arrenquen per ser testejats i depurats sota les condicions més pròximes a la màxima velocitat de treball del SoC. (L'emulació va generalment precedida d'una àmplia simulació per programari, de fet, els FPGAs són usats principalment per accelerar alguna part concreta del procés de simulació).

Després de l'emulació satisfactòria del maquinari del SoC, es procedeix a la fase de posicionament i encaminat de la circuiteria (per a això s'utilitzen aplicacions CAD, com ja s'ha dit abans), obtenint el disseny més òptim per a la seva fabricació en sèrie.

Els xips són testejats i verificats per possibles correccions lògiques abans d'enviar a fosa definitivament. Aquesta tasca s'anomena verificació funcional, i garanteix uns correctes funcionament, temps d'operació i energia consumida, durant gran part del seu cicle de vida (encara que el percentatge del 70% sovint assegurat pel fabricant és exagerat).[4]

HDLs com Verilog o VHDL són eines comunament usades en el procés de verificació. A causa de la creixent complexitat dels xips, s'estan començant a usar HDLs més avançats com són SystemVerilog, SystemC, i (llenguatge de verificació), o OpenVera. Els bugs trobats durant la verificació són redactats en un informe enviat al dissenyador, per la seva corresponent reparació.

Fabricació

[modifica]Els SoCs poden ser fabricats utilitzant diferents tecnologies, incloent:

- Disseny a mida (full custom)

- Disseny basat en Cel·les Estàndard (standard cell)

- Disseny basat en 'Field-programmable gate array' so FPGAs

Un SoC normalment consumeix menys energia, té un cost inferior i una major fiabilitat que els sistemes multi-xip als que acaben reemplaçant. Així doncs, amb menys peces necessàries per al sistema, els costos de material i acoblament es veuen reduïts.[5]

Tanmateix, com en molts projectes VLSI, el cost total inicial és superior per a un xip més gran que per a la mateixa funcionalitat distribuïda en xips més petits, a causa a rendiments més baixos per la reduïda grandària de la tecnologia de fabricació, més propensa a errors, i uns costos NRE més elevats (els costos NRE poden entendre com la inversió inicial per al desenvolupament, investigació, fabricació i testeig d'un producte nou, capital susceptible de no ser recuperat en no estar assegurat el volum mínim de vendes per a la rendibilitat del producte).

Referències

[modifica]- ↑ Pete Bennett, EE Times. "The why, where and what of low-power SoC design." December 2, 2004. Retrieved July 28, 2015.

- ↑ articleID = 159901628 The Great Debat: SOC vs. SIP. Eetimes.com.

- ↑ Carroll & Heiser (2010) "An Analysis of Power Consumption in a Smartphone", Usenix

- ↑ Is verification really 70 percent?. Eetimes.com.

- ↑ Brian Bailey, EE Times. "Tektronix hopes to shake up ASIC prototyping." October 30, 2012

Vegeu també

[modifica]Enllaços externs

[modifica]- SOCC Annual IEEE International SOC Conference

- La tecnologia System-on-chip en la seva majoria d'edat

- Optimització d'energia a nivell de sistema (System-level power optimization)

- Application Processor