Arquitectura Clipper

| Fabricant | Fairchild Semiconductor |

|---|---|

| Característiques de CPUs | |

| Conjunt d'instruccions | Arquitectura de conjunt d'instruccions RISC |

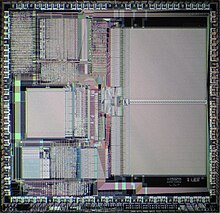

L'arquitectura Clipper és una arquitectura de conjunt d'instruccions semblant a RISC de 32 bits dissenyada per Fairchild Semiconductor. L'arquitectura mai va tenir molt èxit de mercat, i els únics fabricants d'ordinadors que van crear grans línies de productes utilitzant processadors Clipper van ser Intergraph i High Level Hardware, tot i que Opus Systems va oferir un producte basat en el Clipper com a part de la seva gamma Personal Mainframe. Els primers processadors que utilitzaven l'arquitectura Clipper van ser dissenyats i venuts per Fairchild, però la divisió responsable d'ells es va vendre posteriorment a Intergraph el 1987; Intergraph va continuar treballant en els processadors Clipper per utilitzar-los en els seus propis sistemes.[1]

L'arquitectura Clipper utilitzava un conjunt d'instruccions simplificat en comparació amb les arquitectures CISC anteriors, però sí que incorporava algunes instruccions més complicades que les que hi havia en altres processadors RISC contemporanis. Aquestes instruccions es van implementar en una anomenada Macro Instruction ROM dins de la CPU Clipper. Aquest esquema va permetre que el Clipper tingués una densitat de codi una mica més alta que altres CPU RISC.[2]

Versions

[modifica]El microprocessador Clipper inicial produït per Fairchild va ser el C100, que va estar disponible el 1986. Aquest va ser seguit pel C300 més ràpid d'Intergraph el 1988. El model final del Clipper va ser el C400, llançat el 1990, que va ser àmpliament redissenyat per ser més ràpid i afegir més registres de coma flotant. El processador C400 va combinar dues tècniques arquitectòniques clau per aconseguir un nou nivell de rendiment: enviament d'instruccions superescalar i operació superpipeline.

Intergraph va començar a treballar en un disseny posterior del processador Clipper conegut com el C5, però mai no es va completar ni es va publicar. No obstant això, es van idear algunes tècniques avançades de disseny de processadors per al C5, i Intergraph va obtenir patents sobre aquestes. Aquestes patents, juntament amb les patents originals de Clipper, han estat la base de les demandes per infracció de patents d'Intergraph contra Intel i altres empreses.[3]

Registres i conjunt d'instruccions

[modifica]El Clipper té 16 registres enters (R15 s'utilitza com a punter de pila), 16 registres de coma flotant (limitat a 8 en les primeres implementacions), més un comptador de programa (PC), una paraula d'estat del processador (PSW) que conté l'estat ALU i FPU senyals i activacions de trampes, i una paraula d'estat del sistema (SSW) que conté l'habilitació d'interrupció externa, el mode d'usuari/supervisor i els bits de control de traducció d'adreces.[4]

Els modes d'usuari i supervisor tenen bancs separats de registres enters. El maneig d'interrupcions va consistir en desar el PC, el PSW i el SSW a la pila, esborrar el PSW i carregar el PC i el SSW des d'un vector de trampa de memòria.

El Clipper és una arquitectura de càrrega/emmagatzematge, on les operacions aritmètiques només podrien especificar operands de registre o immediats. La instrucció bàsica "paquet" és de 16 bits: 8 bits de codi operatiu, 4 bits de registre d'origen i 4 bits de registre de destinació. Els formularis d'operands immediats permeten que 1 o 2 paquets d'instruccions següents especifiquen un operand immediat de 16 bits (estès de signe) o de 32 bits. El processador és uniformement little-endian, inclosos els operands immediats.

Referències

[modifica]- ↑ Weisberg, David. «The Engineering Design Revolution: The People, Companies and Computer Systems That Changed Forever the Practice of Engineering» (en english). Arxivat de l'original el 4 March 2016. [Consulta: 26 juny 2016].

- ↑ «Clipper: A Low-Latency Online Prediction Serving System» (en anglès). [Consulta: 3 octubre 2024].

- ↑ Flynn, Laurie. «Intergraph And Intel Settle Chip Dispute» (en english). The New York Times, 31-03-2004. Arxivat de l'original el 19 June 2015. [Consulta: 26 juny 2016].

- ↑ «Clipper» (en anglès americà). [Consulta: 3 octubre 2024].