Divisor de freqüència

Un divisor de freqüència, també anomenat divisor de rellotge (scaler o prescaler), és un circuit que agafa un senyal d'entrada d'una freqüència, , i genera un senyal de sortida d'una freqüència submúltiple:

on és un nombre enter. Els sintetitzadors de freqüència de bucle bloquejats en fase fan servir divisors de freqüència per generar una freqüència que és múltiple d'una freqüència de referència. Els divisors de freqüència es poden implementar tant per a aplicacions analògiques com digitals.

Analògic

[modifica]Els divisors de freqüència analògics són menys comuns i només s'utilitzen per a freqüències molt altes. Els divisors digitals implementats en les tecnologies IC modernes poden funcionar fins a desenes de GHz.[1]

Regeneratiu

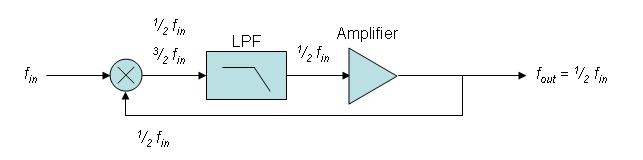

[modifica]Un divisor de freqüència regeneratiu, també conegut com a divisor de freqüència de Miller,[2] barreja el senyal d'entrada amb el senyal de retroalimentació del mesclador.

El senyal de retroalimentació és . Això produeix freqüències de suma i diferència , a la sortida del mesclador. Un filtre de pas baix elimina la freqüència més alta i el La freqüència s'amplifica i es torna a alimentar al mesclador.

Bloqueig per injecció

[modifica]Un oscil·lador de funcionament lliure que tingui una petita quantitat d'un senyal de freqüència més alta tendirà a oscil·lar al mateix temps que el senyal d'entrada. Aquests divisors de freqüència van ser essencials en el desenvolupament de la televisió.

Funciona de manera similar a un oscil·lador bloquejat per injecció. En un divisor de freqüència bloquejat per injecció, la freqüència del senyal d'entrada és un múltiple (o fracció) de la freqüència de funcionament lliure de l'oscil·lador. Tot i que aquests divisors de freqüència solen tenir una potència més baixa que els divisors de freqüència estàtics de banda ampla (o basats en flip-flop), l'inconvenient és el seu baix rang de bloqueig. El rang de bloqueig ILFD és inversament proporcional al factor de qualitat (Q) del tanc de l'oscil·lador. En els dissenys de circuits integrats, això fa que un ILFD sigui sensible a les variacions del procés. S'ha de tenir cura de garantir que el rang de sintonització del circuit de conducció (per exemple, un oscil·lador controlat per tensió) ha d'estar dins del rang de bloqueig d'entrada de l'ILFD.

Digital

[modifica]

Per a la divisió de potència de 2 sencers, es pot utilitzar un comptador binari senzill, marcat pel senyal d'entrada. El bit de sortida menys significatiu s'alterna a 1/2 de la velocitat del rellotge d'entrada, el bit següent a 1/4 de la velocitat, el tercer bit a 1/8 de la velocitat, etc. Una disposició de flipflops és un mètode clàssic per a la divisió n enter. Aquesta divisió és la freqüència i la fase coherents a la font sobre les variacions ambientals, inclosa la temperatura. La configuració més senzilla és una sèrie on cada Flip-Flop dividideix per 2. Per a una sèrie de tres d'aquests, aquest sistema seria una divisió per 8. Afegint portes lògiques addicionals a la cadena de flip-flops, es poden obtenir altres proporcions de divisió. Les famílies lògiques de circuits integrats poden proporcionar una solució d'un sol xip per a algunes relacions de divisió comunes.[3]

Un altre circuit popular per dividir un senyal digital per un múltiple enter parell és un comptador de Johnson. Aquest és un tipus de xarxa de registre de desplaçament que està marcada pel senyal d'entrada. La sortida complementada de l'últim registre es retorna a l'entrada del primer registre. El senyal de sortida es deriva d'una o més de les sortides del registre. Per exemple, un divisor dividit per 6 es pot construir amb un comptador Johnson de 3 registres. Els sis valors vàlids del comptador són 000, 100, 110, 111, 011 i 001. Aquest patró es repeteix cada vegada que el senyal d'entrada marca la xarxa. La sortida de cada registre és una ona quadrada f/6 amb 120° de desfasament entre registres. Es poden afegir registres addicionals per proporcionar divisors enters addicionals.

Senyal mixt

[modifica](AP: lògica seqüencial)

Una disposició de Flip-Flops D és un mètode clàssic per a la divisió n enter. Aquesta divisió és la freqüència i la fase coherents a la font sobre les variacions ambientals, inclosa la temperatura. La configuració més senzilla és una sèrie on cada Flip-Flop D és dividida per 2. Per a una sèrie de tres d'aquests, aquest sistema seria una divisió per 8. S'han trobat configuracions més complicades que generen factors estranys, com ara una divisió per 5. Els xips lògics estàndard i clàssics que implementen aquestes funcions de divisió de freqüència o similars inclouen els 7456, 7457, 74292 i 74294. (vegeu la llista de la sèrie 7400 i la llista de xips lògics de la sèrie 4000 )

Síntesi fraccional-n

[modifica]Un sintetitzador de freqüència n-fraccional es pot construir utilitzant dos divisors enters, un divisor de freqüència per n i un divisor de freqüència dividit per (n +1). Amb un controlador modular, n es commuta entre els dos valors de manera que el VCO alterni entre una freqüència bloquejada i l'altra. El VCO s'estabilitza a una freqüència que és la mitjana de temps de les dues freqüències de bloqueig. En variar el percentatge de temps que el divisor de freqüència passa als dos valors del divisor, la freqüència del VCO bloquejat es pot seleccionar amb una granularitat molt fina.

Delta-sigma

[modifica]Si la seqüència de dividir per n i dividir per (n + 1) és periòdica, apareixen senyals falsos a la sortida del VCO a més de la freqüència desitjada. Els divisors fraccionals-n Delta-sigma superen aquest problema mitjançant l'aleatorització de la selecció de n i (n + 1) mentre mantenen les proporcions mitjanes del temps.

Referències

[modifica]- ↑ «Figure 5: Block diagram of the frequency divider design. Each...». [Consulta: 30 juliol 2023].

- ↑ R. L. Miller Proceedings of the IRE, 27, 7, 1939, pàg. 446–457. DOI: 10.1109/JRPROC.1939.228513.

- ↑ Storr, Wayne. «Frequency Division using Divide-by-2 Toggle Flip-flops», 01-08-2013. [Consulta: 30 juliol 2023].

Bibliografia

[modifica]- Contemporary Logic Design. 2a edició. Prentice Hall, 2005. ISBN 0-201-30857-6.

- Switching and Finite Automata Theory. 3. Cambridge University Press, 2009. ISBN 978-0-521-85748-2.

- «Asynchronous logic elements. Venjunction and sequention», 2009. Arxivat de l'original el 2011-07-22. (118 pages)

- Asynchronous Operators of Sequential Logic: Venjunction & Sequention — Digital Circuits Analysis and Design. 101. Riga, Latvia: Springer-Verlag, 2011. DOI 10.1007/978-3-642-21611-4. ISBN 978-3-642-21610-7. LCCN 2011929655. (xiii+1+123+7 pages) (NB. The back cover of this book erroneously states volume 4, whereas it actually is volume 101.)