Pentium (original)

| Marca | Pentium |

|---|---|

| Desenvolupador | Intel |

| Fabricant | Intel |

| Característiques de CPUs | |

| Conjunt d'instruccions | x86-64 |

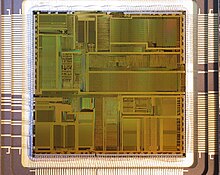

El Pentium (també conegut com a i586) és un microprocessador x86 introduït per Intel el 22 de març de 1993. És la primera CPU que utilitza la marca Pentium. Considerada la cinquena generació de la línia de processadors compatibles 8086, la seva implementació i microarquitectura s'anomenava internament P5.[1]

Igual que l'Intel i486, el Pentium és un conjunt d'instruccions compatible amb el 80386 de 32 bits. Utilitza una microarquitectura molt similar a l'i486, però s'ha ampliat prou com per implementar un disseny de canalització de nombre enter dual, així com una unitat de coma flotant més avançada. La primera és una cosa que s'havia argumentat que era impossible d'implementar per a un conjunt d'instruccions del CISC, per part de certs acadèmics i competidors del RISC.[2]

El P5 Pentium és el primer processador x86 superescalar, el que significa que sovint era capaç d'executar dues instruccions al mateix temps. Algunes tècniques utilitzades per implementar-ho es van basar en l'anterior Intel i960 CA superescalar (1989), mentre que altres detalls es van inventar exclusivament per al disseny P5. També es van copiar grans peces de l'i386 o i486, especialment les estratègies utilitzades per fer front a les complicades codificacions x86 d'una manera canalitzada. Igual que l'i486, el Pentium utilitzava tant un sistema de microcodi optimitzat com tècniques semblants a RISC, depenent de la instrucció en particular, o part de la instrucció.[3]

Altres característiques centrals inclouen una unitat de coma flotant redissenyada i significativament més ràpida, un ampli bus de dades de 64 bits (extern i intern), memòria cau de dades i codi separats i moltes altres tècniques i funcions per millorar el rendiment.

El P5 també té un millor suport per al multiprocessament en comparació amb l'i486, i és la primera CPU x86 amb suport de maquinari similar als ordinadors mainframe IBM. Intel va treballar amb IBM per definir aquesta capacitat i també la va dissenyar a la microarquitectura P5. Aquesta capacitat estava absent a les generacions anteriors x86 i als processadors x86 dels competidors.

Per tal d'utilitzar les canalitzacions duals al seu màxim potencial, es van optimitzar determinats compiladors per explotar millor el paral·lelisme a nivell d'instrucció, encara que no totes les aplicacions tindrien un benefici substancial amb la recompilació. Tanmateix, la FPU més ràpida sempre va millorar significativament el rendiment del punt flotant, en comparació amb l'i486 o i387. Intel va gastar recursos treballant amb proveïdors d'eines de desenvolupament, ISV i empreses de sistemes operatius (SO) per optimitzar els seus productes.

L'octubre de 1996, es va introduir el Pentium MMX similar, complementant la mateixa microarquitectura bàsica amb el conjunt d'instruccions MMX, memòria cau més gran i algunes altres millores.[4]

Desenvolupament

[modifica]La microarquitectura P5 va ser dissenyada pel mateix equip de Santa Clara que va dissenyar els 386 i 486. El treball de disseny va començar l'any 1989; l'equip va decidir utilitzar una arquitectura superescalar, amb memòria cau en xip, punt flotant , i predicció de branques. El disseny preliminar es va simular amb èxit per primera vegada el 1990, seguit de la disposició del disseny. En aquest moment, l'equip tenia diverses desenes d'enginyers. El disseny es va gravar, o es va transferir a silici, l'abril de 1992, moment en què van començar les proves beta. A mitjans de 1992, l'equip P5 tenia 200 enginyers. Intel inicialment tenia previst demostrar el P5 el juny de 1992 a la fira PC Expo, i anunciar formalment el processador el setembre de 1992, però el disseny problemes van obligar a cancel·lar la demostració i la introducció oficial del xip es va retardar fins a la primavera de 1993.

Millores respecte a l'i486

[modifica]La microarquitectura P5 aporta diversos avenços importants respecte a l'arquitectura i486 anterior.

- Arquitectura superescalar: el Pentium té dos camins de dades (conductes) que li permeten completar dues instruccions per cicle de rellotge en molts casos. La canonada principal (U) pot gestionar qualsevol instrucció, mentre que l'altra (V) pot gestionar les instruccions simples més habituals. Alguns defensors de l'ordinador del conjunt d'instruccions reduïts (RISC) havien argumentat que el conjunt d'instruccions x86 "complicat" probablement mai no s'implementaria mitjançant una microarquitectura estretament canalitzada, i molt menys amb un disseny de canalització dual. El 486 i el Pentium van demostrar que això era realment possible i factible.

- El bus de dades extern de 64 bits duplica la quantitat d'informació que es pot llegir o escriure a cada accés a la memòria i, per tant, permet que el Pentium carregui la seva memòria cau de codi més ràpid que el 80486; també permet un accés i emmagatzematge més ràpids de dades de FPU x87 de 64 i 80 bits. La separació de la memòria cau de codi i de dades redueix els conflictes de lectura/escriptura de recuperació i operand en comparació amb el 486. Per reduir el temps d'accés i el cost d'implementació, tots dos són associatius de 2 vies, en lloc de la memòria cau única de 4 vies del 486. A La millora relacionada amb el Pentium és la capacitat de llegir un bloc contigu de la memòria cau de codi fins i tot quan es divideix entre dues línies de memòria cau (almenys 17 bytes en el pitjor dels casos). Unitat de coma flotant molt més ràpida. Algunes instruccions van mostrar una millora enorme, sobretot FMUL, amb un rendiment fins a 15 vegades superior al de la FPU 80486.

- El Pentium també és capaç d'executar una instrucció FXCH ST(x) en paral·lel amb una instrucció FPU ordinària (aritmètica o de càrrega/emmagatzematge). Els sumadors d'adreces de quatre entrades permeten que el Pentium redueixi encara més la latència de càlcul d'adreces en comparació amb el 80486. El Pentium pot calcular modes d'adreçament complets amb segment-base + base-registre + registre escalat + desplaçament immediat en un sol cicle; el 486 només té un sumador d'adreces de tres entrades i, per tant, ha de dividir aquests càlculs entre dos cicles. El microcodi pot utilitzar ambdues canalitzacions per permetre que les instruccions de repetició automàtica, com ara REP MOVSW, realitzin una iteració cada cicle de rellotge, mentre que el 80486 necessitava tres rellotges per iteració (i els primers xips x86 significativament més que el 486).

- A més, l'optimització de l'accés a les primeres paraules de microcodi durant les etapes de descodificació ajuda a fer que diverses instruccions freqüents s'executin significativament més ràpidament, especialment en les seves formes més habituals i en casos típics. Alguns exemples són (486→Pentium, en cicles de rellotge): CALL (3→1), RET (5→2), canvia/gira (2–3→1). Un multiplicador més ràpid i totalment basat en maquinari fa que instruccions com MUL i IMUL siguin diverses vegades més ràpides (i més previsibles) que al 80486; el temps d'execució es redueix de 13 a 42 cicles de rellotge fins a 10-11 per a operands de 32 bits. Interrupció virtualitzada per accelerar el mode 8086 virtual.

- Predicció de branca

- El posterior Pentium MMX també va afegir el conjunt d'instruccions MMX, una extensió de conjunt d'instruccions d'instrucció senzilla entera, múltiples dades (SIMD) comercialitzada per al seu ús en aplicacions multimèdia. MMX no es va poder utilitzar simultàniament amb les instruccions de la FPU x87 perquè els registres es van reutilitzar (per permetre canvis de context ràpids). Les millores més importants van ser la duplicació de la mida de la memòria cau d'instruccions i dades i alguns canvis microarquitectònics per a un millor rendiment.

Referències

[modifica]- ↑ «The Pentium: An Architectural History of the World’s Most Famous Desktop Processor (Part I)» (en anglès). [Consulta: 8 gener 2024].

- ↑ «Explore Intel’s history- The Birth of Pentium» (en anglès). [Consulta: 8 gener 2024].

- ↑ «The Intel Pentium: A quick look back at the landmark PC processor for its 30th anniversary» (en anglès), 08-01-2024. [Consulta: 8 gener 2024].

- ↑ published, The Editors of Tom's Hardware. «Intel drops "Pentium" brand» (en anglès), 15-01-2006. [Consulta: 8 gener 2024].