Ruta de dades

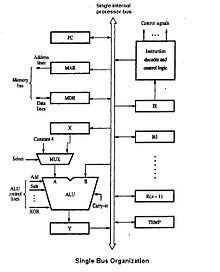

Una ruta de dades és una col·lecció d'unitats funcionals com ara unitats aritmètiques lògiques (ALU) o multiplicadors que realitzen operacions de processament de dades, registres i busos. Juntament amb la unitat de control forma la unitat central de processament (CPU). Es pot fer una ruta de dades més gran unint més d'una ruta de dades mitjançant multiplexors.[1]

Una ruta de dades és l'ALU, el conjunt de registres i els busos interns de la CPU que permeten que les dades flueixin entre ells.

El disseny més senzill per a una CPU utilitza un bus intern comú. Una addició eficient requereix una estructura de tres busos interns una mica més complicada. Moltes CPU relativament senzilles tenen un fitxer de registre de 2 lectures i 1 escriptura connectat a les 2 entrades i 1 sortida de l'ALU.

A finals de la dècada de 1990, hi va haver una investigació creixent en l'àrea de camins de dades reconfigurables, camins de dades que es poden reutilitzar en temps d'execució mitjançant teixit programable, ja que aquests dissenys poden permetre un processament més eficient i un estalvi d'energia substancial.[2]

Màquina d'estats finits amb ruta de dades

[modifica]Una màquina d'estats finits amb ruta de dades (FSMD) és una abstracció matemàtica que combina una màquina d'estats finits, que controla el flux del programa, amb una ruta de dades. Es pot utilitzar per dissenyar lògica digital o programes informàtics.[3][4]

Els FSMD són essencialment programes seqüencials en els quals les declaracions s'han programat en estats, donant lloc a diagrames d'estats més complexos. Aquí, un programa es converteix en un diagrama d'estat complex en el qual els estats i els arcs poden incloure expressions aritmètiques, i aquestes expressions poden utilitzar entrades i sortides externes, així com variables. El nivell d'abstracció FSMD es coneix sovint com el nivell de transferència de registre.

Els FSM no utilitzen variables ni operacions/condicions aritmètiques, per tant els FSMD són més potents que els FSM. Un FSMD és equivalent a una màquina de Turing en expressivitat.

Referències

[modifica]- ↑ «What is a Data Path?» (en anglès). [Consulta: 24 novembre 2024].

- ↑ J. R. Hauser and J. Wawrzynek, Garp: a MIPS processor with a reconfigurable coprocessor, FCCM’97, 1997, pp. 12–21.

- ↑ Zhu, Jianwen. «A unified formal model of ISA and FSMD». A: Proceedings of the seventh international workshop on Hardware/Software codesign - CODES '99 (en anglès). New York, NY, USA: Association for Computing Machinery, 1999-03-01, p. 121–125. DOI 10.1145/301177.301504. ISBN 978-1-58113-132-1.

- ↑ Hsu, Y.C.. «Digital design from concept to prototype in hours». A: Proceedings of APCCAS'94 - 1994 Asia Pacific Conference on Circuits and Systems (en anglès), 1994-12-05, p. 175–181. DOI 10.1109/APCCAS.1994.514545. ISBN 0-7803-2440-4.