Tensió llindar

La tensió llindar, abreujada comunament com a V th, d'un transistor d'efecte de camp (FET) és la tensió mínima de la porta a la font V GS (th) que es necessita per crear un camí conductor entre els terminals de font i drenatge. És un factor d'escala important per mantenir l'eficiència energètica.[2][3]

Quan es fa referència a un transistor d'efecte de camp d'unió (JFET), la tensió de llindar sovint s'anomena tensió de pinch-off (pessigament, permet la modulació de longitud de canal).[4][5] Això és una mica confús, ja que el pessic aplicat al transistor d'efecte de camp de la porta aïllada (IGFET) es refereix al pessigament del canal que condueix a un comportament de saturació actual sota un alt biaix de drenatge de font, tot i que el corrent mai no s'apaga. A diferència de pinch-off, el terme tensió llindar és inequívoc i fa referència al mateix concepte en qualsevol transistor d'efecte de camp.[6]

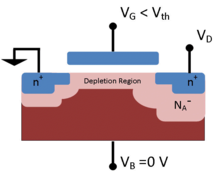

Si la tensió de la porta està per sota de la tensió llindar (figura 2), el transistor "mode de millora" s'apaga i, idealment, no hi ha corrent des del drenatge a la font del transistor. De fet, hi ha un corrent fins i tot per als biaixos de la porta per sota del corrent llindar (fuga subllindar), tot i que és petit i varia exponencialment amb el biaix de la porta.Si la tensió de la porta està per sobre de la tensió llindar (figura 3), el transistor de "mode de millora" s'activa, ja que hi ha molts electrons al canal a la interfície òxid-silici, creant un canal de baixa resistència on la càrrega pot flueix del desguàs a la font. Per a tensions significativament per sobre del llindar, aquesta situació s'anomena inversió forta. El canal es redueix quan VD > 0 perquè la caiguda de tensió a causa del corrent al canal resistiu redueix el camp d'òxid que suporta el canal a mesura que s'acosta al drenatge.

Referències

[modifica]- ↑ Kim, SungGeun;Luisier «OMEN Nanowire». Full-band 3D quantum transport simulation in nanowire structure, 2008. DOI: 10.21981/SX3C-YN45.

- ↑ Lancaster, David. «Threshold voltage of a MOSFET» (en anglès). https://electronicguidebook.com,+09-04-2022.+[Consulta: 2 octubre 2022].

- ↑ «Low Voltage Logic Thresholds Chart, IC Switching Levels» (en anglès). http://www.interfacebus.com.+[Consulta: 2 octubre 2022].

- ↑ «Junction Field Effect Transistor (JFET)» (en anglès). ETEE3212 Lecture Notes. Arxivat de l'original el 2022-10-09. [Consulta: 2 octubre 2022].

- ↑ Sedra, Adel S. «5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)». A: Microelectronic Circuits (en anglès). https://global.oup.com,+2-10-2022.

- ↑ «[https://global.oup.com/us/companion.websites/fdscontent/uscompanion/us/static/companion.websites/9780199339136/pdf/bonustopics.pdf JFETs, GaAs DEVICES AND CIRCUITS, AND TTL CIRCUITS 1 5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)]» (en anglès). https://global.oup.com.+[Consulta: 20 febrer 2022].