Traça memòria cau

A l'arquitectura d'ordinadors, una memòria cau de traça o memòria cau de traça d'execució és una memòria cau d'instruccions especialitzada que emmagatzema el flux dinàmic d'instruccions conegut com traça. Ajuda a augmentar l'ample de banda d'obtenció d'instruccions i a reduir el consum d'energia (en el cas d'Intel Pentium 4) emmagatzemant rastres d'instruccions que ja s'han obtingut i descodificat.[1] Un processador de traça és una arquitectura dissenyada al voltant de la memòria cau de traça i processa les instruccions a nivell de granularitat de traça. La teoria matemàtica formal de traces es descriu per traces monoides.[2]

Rerefons

[modifica]La publicació acadèmica més antiga de la memòria cau de traça va ser "Trace Cache: a Low Latency Approach to High Bandwidth Instruction Fetching".[3] Aquest document àmpliament reconegut va ser presentat per Eric Rotenberg, Steve Bennett i Jim Smith a la conferència de 1996 International Symposium on Microarchitecture (MICRO). Una publicació anterior és la patent nord-americana 5381533, d'Alex Peleg i Uri Weiser d'Intel, "Dynamic flow instruction cache memory organized around trace segments independent of virtual address line", una continuació d'una sol·licitud presentada el 1992, més tard abandonada.

Necessitat

[modifica]Els processadors superescalars més amplis demanen que s'obtinguin múltiples instruccions en un sol cicle per obtenir un rendiment superior. Les instruccions que s'han d'obtenir no sempre es troben en ubicacions de memòria contigües (blocs bàsics) a causa de les instruccions de ramificació i salt. Per tant, els processadors necessiten suport addicional de lògica i maquinari per obtenir i alinear aquestes instruccions de blocs bàsics no contigus

. Si es preveu que diverses branques no es prenen, els processadors poden obtenir instruccions de diversos blocs bàsics contigus en un sol cicle. Tanmateix, si es preveu que alguna de les branques sigui presa, el processador hauria d'obtenir instruccions del camí pres en aquest mateix cicle. Això limita la capacitat d'obtenció d'un processador.

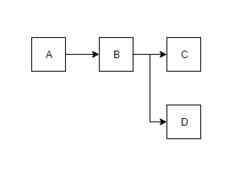

Considereu aquests quatre blocs bàsics (A,B,C,D) tal com es mostra a la figura que corresponen a un simple bucle if-else. Aquests blocs s'emmagatzemaran de manera contigua com ABCD a la memòria. Si es preveu que la branca D no s'ha pres, la unitat de recuperació pot obtenir els blocs bàsics A, B, C que es col·loquen de manera contigu. Tanmateix, si es prediu que D es pren, la unitat d'obtenció ha de buscar A, B, D que no estan col·locats de manera contigua. Per tant, aconseguir aquests blocs que no estan col·locats de manera contigu, en un sol cicle serà molt difícil. Per tant, en situacions com aquestes, la memòria cau de traça ajuda el processador.

Un cop obtinguda, la memòria cau de traça emmagatzema les instruccions en la seva seqüència dinàmica. Quan es tornen a trobar aquestes instruccions, la memòria cau de traça permet que la unitat d'obtenció d'instruccions d'un processador obtingui diversos blocs bàsics sense haver de preocupar-se per les branques del flux d'execució. Les instruccions s'emmagatzemaran a la memòria cau de traça després d'haver estat descodificades o quan es retirin. Tanmateix, la seqüència d'instruccions és especulativa si s'emmagatzemen just després de l'etapa de descodificació.

Disseny de la memòria cau de traça

[modifica]A continuació es mostren els factors que cal tenir en compte a l'hora de dissenyar una memòria cau de traça.

- Polítiques de selecció de traça: nombre màxim d'instruccions i blocs bàsics màxims en una traça

- Associativitat: nombre de maneres que pot tenir una memòria cau

- Mètode d'indexació de la memòria cau: concatenació o XOR amb bits de PC

- Associativitat del camí: les traces amb el mateix ordinador inicial però amb diferents blocs bàsics es poden assignar a diferents conjunts

- Traça les opcions d'ompliment de la memòria cau -

- # Després de l'etapa de descodificació (especulativa)

- # Després de l'etapa de jubilació

Una memòria cau de traça no es troba al camí crític de la recuperació d'instruccions [4]

Referències

[modifica]- ↑ Rotenberg, Eric; Bennett, Steve; Smith, James E.; Rotenberg, Eric In Proceedings of the 29th International Symposium on Microarchitecture, 01-01-1996, pàg. 24–34.

- ↑ «Trace Cache: a Low Latency Approach to High Bandwidth Instruction Fetching» (en anglès). [Consulta: 23 març 2024].

- ↑ Rotenberg, Eric; Bennett, Steve; Smith, James E.; Rotenberg, Eric In Proceedings of the 29th International Symposium on Microarchitecture, 01-01-1996, pàg. 24–34.

- ↑ Leon Gu; Dipti Motiani (October 2003). "Trace Cache" (PDF). Retrieved2013-10-06.