Usuari:Castor/Traduccions2

An analog-to-digital converter (abbreviated ADC, A/D or A to D) is a device which converts a continuous quantity to a discrete digital number. The reverse operation is performed by a digital-to-analog converter (DAC).

Un convertidor analògic/digital (abreujat Adc, A/D o A a D) és un mecanisme que converteix una quantitat contínua en un discret número digital. L'operació inversa és executada per un convertidor digital/analògic (( Dac)).

Typically, an ADC is an electronic device that converts an input analog voltage (or current) to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs.

Típicament, un Adc és un mecanisme electrònic que converteix una entrada voltatge analògic (o corrent) a un número digital proporcional a la magnitud del voltatge o actual. Tanmateix, alguns mecanismes no electrònics o només parcialment electrònics, com codificadors rotatius, també es poden considerar Adcs.

The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.

La sortida digital pot utilitzar esquemes de codificació diferents. Típicament la sortida digital serà un complement de two's número binari que és proporcional a l'entrada, però allà són unes altres possibilitats. Un codificador, per exemple, podria imprimir un Codi gris.

An ADC may provide an isolated measurement. ADCs are also used in quantization of time-varying signals by turning them into a sequence of digital samples. The result is quantized in both time and value.

Un Adc pot proporcionar una mesura aïllada. Els Adcs també s'utilitzen en la quantització de time-varying signals convertint-los en una seqüència de mostres digitals. El resultat es quantized tant en temps com en valor.

Conceptes

[modifica]Resolution

[modifica]250px|polze|Xifra 1. Un esquema de codificació d'Adc de 8 nivell.

250px|polze|Xifra 3. Un esquema de codificació mig estesa d'Adc de 8 nivell. Com en la xifra 2 però amb igual half- Lsb intervals als codis més alts i més baixos. Nota que Lsb és ara una mica més gran que en xifres 1 i 2. The resolution of the converter indicates the number of discrete values it can produce over the range of analog values. The values are usually stored electronically in binary form, so the resolution is usually expressed in bits. In consequence, the number of discrete values available, or "levels", is usually a power of two. For example, an ADC with a resolution of 8 bits can encode an analog input to one in 256 different levels, since 28 = 256. The values can represent the ranges from 0 to 255 (i.e. unsigned integer) or from −128 to 127 (i.e. signed integer), depending on the application.

La resolució del convertidor indica el número de valors discrets que pot produir sobre la gamma de valors analògics. Els valors s'emmagatzemen normalment electrònicament en forma binària, així la resolució s'expressa normalment en miques. En conseqüència, el número de valors discrets disponibles, o "nivells", és normalment un poder de dos. Per exemple, un Adc amb una resolució de 8 miques pot codificar una entrada analògica a un en 256 nivells diferents, des de 28 = 256. Els valors poden transmetre les gammes des de 0 a 255 (i.e. enter insignat) o des de −128 a 127 (enter i.e. signat), depenent de l'aplicació.

Resolution can also be defined electrically, and expressed in volts. The minimum change in voltage required to guarantee a change in the output code level is called the LSB (least significant bit, since this is the voltage represented by a change in the LSB). The resolution Q of the ADC is equal to the LSB voltage. The voltage resolution of an ADC is equal to its overall voltage measurement range divided by the number of discrete voltage intervals:

La resolució també es pot definir elèctricament, i expressar-se en volts. El canvi mínim a voltatge exigia que per garantir es cridi un canvi al nivell de codi de sortida el Lsb (bit de mínima significació, ja que aquest és el voltatge representat per un canvi al Lsb). La resolució Q de l'Adc és igual al Lsb voltatge. La resolució de voltatge d'un Adc és igual a la seva gamma de mesura de voltatge global dividit pel número d'intervals de voltatge discrets:

where N is the number of voltage intervals and EFSR is the full scale voltage range. EFSR is given by

on N és el número d'intervals de voltatge i E Fsr és la plena gamma de voltatge d'escala. E Fsr és donat per

where VRefHi and VRefLow are the upper and lower extremes, respectively, of the voltages that can be coded.

on V RefHi i V RefLow són els extrems superiors i més baixos, respectivament, dels voltatges que es poden codificar.

Normally, the number of voltage intervals is given by

Normalment, el número d'intervals de voltatge es dóna a prop

where M is the ADC's resolution in bits.

on M és la resolució de l'Adc en miques.

That is, one voltage interval is assigned per code level. However, figure 3 shows a situation where

És a dir, un interval de voltatge s'assigna per nivell de codi. Tanmateix, figuri 3 espectacles una situació on

Some examples:

Alguns exemples:

- Example 1

- Exemple 1

- Coding scheme as in figure 1

Esquema de Codificació de ** com en la xifra 1

- Full scale measurement range = 0 to 10 volts

Gamma de mesura d'Escala plena de ** = 0 a 10 volts

- ADC resolution is 12 bits: 212 = 4096 quantization levels (codes)

La resolució de ** Adc són 12 miques: La quantització de 212 = 4096 anivella (codis)

- ADC voltage resolution, Q = (10 V − 0 V) / 4096 = 10 V / 4096 ≈ 0.00244 V ≈ 2.44 mV.

Resolució de voltatge de ** Adc Q = (10 V − 0 V) / 4096 = 10 V / 4096 ≈; 0.00244 V ≈ 2.44 mV.

- Example 2

- Exemple 2

- Coding scheme as in figure 2

Esquema de Codificació de ** com en la xifra 2

- Full scale measurement range = -10 to +10 volts

Gamma de mesura d'escala Plena de ** = -10 a volts de +10

- ADC resolution is 14 bits: 214 = 16384 quantization levels (codes)

La resolució de ** Adc són 14 miques: La quantització de 214 = 16384 anivella (codis)

- ADC voltage resolution is, Q = (10 V − (−10 V)) / 16384 = 20 V / 16384 ≈ 0.00122 V ≈ 1.22 mV.

La resolució de voltatge de ** Adc és, Q = (10 V − (−10 V)) / 16384 = 20 V / 16384 ≈; 0.00122 V ≈ 1.22 mV.

- Example 3

- Exemple 3

- Coding scheme as in figure 3

Esquema de Codificació de ** com en la xifra 3

- Full scale measurement range = 0 to 7 volts

Gamma de mesura d'escala Plena de ** = 0 a 7 volts

- ADC resolution is 3 bits: 23 = 8 quantization levels (codes)

La resolució de ** Adc són 3 miques: La quantització de 23 = 8 anivella (codis)

- ADC voltage resolution is, Q = (7 V − 0 V)/7 = 7 V/7 = 1 V = 1000 mV

La resolució de voltatge de ** Adc és, Q = (7 V − 0 V)/7 = 7 V/7 = 1 V = 1000 mV

In most ADCs, the smallest output code ("0" in an unsigned system) represents a voltage range which is 0.5Q, that is, half the ADC voltage resolution (Q). The largest code represents a range of 1.5Q as in figure 2 (if this were 0.5Q also, the result would be as figure 3). The other N − 2 codes are all equal in width and represent the ADC voltage resolution (Q) calculated above. Doing this centers the code on an input voltage that represents the M th division of the input voltage range. This practice is called "mid-tread" operation. This type of ADC can be modeled mathematically as:

En la majoria dels Adcs, el codi de sortida més petit ("0" en un sistema insignat) representa una gamma de voltatge que és 0.5 Q, és a dir, la meitat de la resolució de voltatge Adc (Q) . El codi més gran representa una gamma de 1.5 Q com en la xifra 2 (si això era 0.5 Q també, el resultat seria com la xifra 3). L'altre N −; 2 codis són tot iguals en amplada i representen la resolució de voltatge Adc (Q) comptat a dalt. Fent això centra el codi en un voltatge d'entrada que representa el M divisió de ;th de la gamma de voltatge d'entrada. Aquesta pràctica s'anomena operació de "mid-tread". Aquest tipus d'Adc pot ser modeled matemàticament com:

The exception to this convention seems to be the Microchip PIC processor, where all M steps are equal width, as shown in figure 1. This practice is called "Mid-Rise with Offset" operation.

L'excepció a aquesta convenció sembla que sigui el processador de Pic Microtros, on completament M passos són amplada igual, com mostrada en la xifra 1. Aquesta pràctica s'anomena "Mid-Rise amb Offset" operació.

In practice, the useful resolution of a converter is limited by the best signal-to-noise ratio (SNR) that can be achieved for a digitized signal. An ADC can resolve a signal to only a certain number of bits of resolution, called the effective number of bits (ENOB). One effective bit of resolution changes the signal-to-noise ratio of the digitized signal by 6 dB, if the resolution is limited by the ADC. If a preamplifier has been used prior to A/D conversion, the noise introduced by the amplifier can be an important contributing factor towards the overall SNR.

En la pràctica, la resolució útil d'un convertidor és limitada pel millor signal-to-noise ratio (Snr) que pot ser aconseguit per a un senyal digitalitzat. Un Adc pot resoldre un senyal a només un cert número de miques de resolució, anomenada el número eficaç de miques (Enob). Una mica eficaç de resolució canvia la proporció de signal-to-noise del senyal digitalitzat per 6 dB, si la resolució és limitada per l'Adc. Si un preamplificador s'ha utilitzat abans de conversió d'A/D, el soroll introduït per l'amplificador pot ser un factor que contribueix important cap a la granota Snr.

Response type

[modifica]Linear ADCs

[modifica]Most ADCs are of a type known as linear[1] The term linear implies here the range of the input values that map to each output value has a linear relationship with the output value, i.e., that the output value k is used for the range of input values from

La majoria dels Adcs estan d'un tipus coneguts com[2] El terme lineal implica aquí la gamma dels valors d'entrada que fan que correspondre a cada valor de sortida té una relació lineal amb el valor de sortida, i.e., allò el valor de sortida k és utilitzat perquè la gamma d'entrada valora de

- m(k + b)

- m (k+ b)

to

a

- m(k + 1 + b),

- m (k+ 1 + b)

where m and b are constants. Here b is typically 0 or −0.5. When b = 0, the ADC is referred to as mid-rise, and when b = −0.5 it is referred to as mid-tread.

on m i b són constants. Aquí b és típicament 0 o −0.5. Quan b = 0, l'Adc s'envia a com mig pujada, i quan b = −0.5 és enviat a com mig estesa .

Non-linear ADCs

[modifica]If the probability density function of a signal being digitized is uniform, then the signal-to-noise ratio relative to the quantization noise is the best possible. Because this is often not the case, it is usual to pass the signal through its cumulative distribution function (CDF) before the quantization. This is good because the regions that are more important get quantized with a better resolution. In the dequantization process, the inverse CDF is needed.

Si la funció de densitat de probabilitat d'un senyal que es digitalitza és uniforme, llavors la proporció de signal-to-noise relativa al soroll de quantització és la millor possible. Perquè això és sovint no el cas, és habitual passar el senyal a través de la seva funció de distribució acumulativa (Cdf) abans de la quantització. Això és bo perquè les regions que són més importants es quantized amb una millor resolució. En el procés de dequantization, l'invers Cdf es necessita.

This is the same principle behind the companders used in some tape-recorders and other communication systems, and is related to entropy maximization.

Això és el mateix principi darrere el companders utilitzat en algunes enregistradores de cinta i uns altres sistemes de comunicacions, i es relaciona amb maximització d'entropia.

For example, a voice signal has a Laplacian distribution. This means that the region around the lowest levels, near 0, carries more information than the regions with higher amplitudes. Because of this, logarithmic ADCs are very common in voice communication systems to increase the dynamic range of the representable values while retaining fine-granular fidelity in the low-amplitude region.

Per exemple, un senyal de veu té una Distribució laplaciana. Això significa que la regió al voltant dels nivells més baixos, prop de 0, porti més informació que les regions amb amplituds més altes. A causa d'això, els Adcs logarítmics són molt comuns en sistemes de comunicacions de veu per augmentar la gamma dinàmica dels valors representables mentre retenen fidelitat bé granular a la regió d'amplitud baixa.

An eight-bit A-law or the μ-law logarithmic ADC covers the wide dynamic range and has a high resolution in the critical low-amplitude region, that would otherwise require a 12-bit linear ADC.

Un A-law de vuit mica o el μ;-law cobertes Adc logarítmiques la gamma dinàmica àmplia i té una resolució alta a la regió d'amplitud baixa crítica, allò altrament exigiria una 12 mica Adc lineal.

Accuracy

[modifica]An ADC has several sources of errors. Quantization error and (assuming the ADC is intended to be linear) non-linearity are intrinsic to any analog-to-digital conversion. There is also a so-called aperture error which is due to a clock jitter and is revealed when digitizing a time-variant signal (not a constant value).

Un Adc té unes quantes fonts d'errors. Error de Quantització i (assumint l'Adc està pensat per ser lineal) no-linearity són intrínsec a qualsevol conversió d'analog-to-digital. Hi ha també un anomenat error d'obertures que és a causa d'un nervi de rellotges i és revelat en digitalitzar un senyal variant d'hora (no un valor constant).

These errors are measured in a unit called the LSB, which is an abbreviation for least significant bit. In the above example of an eight-bit ADC, an error of one LSB is 1/256 of the full signal range, or about 0.4%.

Aquests errors es mesuren en una unitat anomenada el Lsb, quina és una abreviatura per a bit de mínima significació. En l'exemple citat d'una vuit mica Adc, un error d'un Lsb és 1/256 de la plena gamma de senyal, o aproximadament un 0.4% .

Quantization error

[modifica]

Quantization error (or quantization noise) is the difference between the original signal and the digitized signal. Hence, The magnitude of the quantization error at the sampling instant is between zero and half of one LSB. Quantization error is due to the finite resolution of the digital representation of the signal, and is an unavoidable imperfection in all types of ADCs.

L'error de quantització (o soroll de quantització) és la diferència entre el senyal original i el senyal digitalitzat. Per això, La magnitud de l'error de quantització a l'instant de mostreig és entre zero i la meitat d'un Lsb. L'error de quantització és a causa de la resolució finita de la representació digital del senyal, i és una imperfecció inevitable en tots els tipus d'Adcs.

Non-linearity

[modifica]All ADCs suffer from non-linearity errors caused by their physical imperfections, causing their output to deviate from a linear function (or some other function, in the case of a deliberately non-linear ADC) of their input. These errors can sometimes be mitigated by calibration, or prevented by testing.

Tots els Adcs pateixen d'errors no-linearity provocats per les seves imperfeccions físiques, fent que la seva sortida es desviï d'una funció lineal (o alguna altra funció, en termes d'un Adc deliberadament no lineal) de la seva entrada. Aquests errors poden a vegades ser mitigats per calibratge, o evitar-se provant.

Important parameters for linearity are integral non-linearity (INL) and differential non-linearity (DNL). These non-linearities reduce the dynamic range of the signals that can be digitized by the ADC, also reducing the effective resolution of the ADC.

Els paràmetres importants per a linearity són integral non-linearity (Inl) i differential non-linearity (Dnl). Aquests no-linearities redueixen la gamma dinàmica dels senyals que es poden digitalitzar per l'Adc, també reduint la resolució eficaç de l'Adc.

Aperture error

[modifica]Imagine that we are digitizing a sine wave . Provided that the actual sampling time uncertainty due to the clock jitter is , the error caused by this phenomenon can be estimated as .

Imagini's que estem digitalitzant una ona de sinus . A condició que el temps de mostreig real incertesa a causa del nervi de rellotges és , l'error provocat per aquest fenomen es pot calcular com .

The error is zero for DC, small at low frequencies, but significant when high frequencies have high amplitudes. This effect can be ignored if it is drowned out by the quantizing error. Jitter requirements can be calculated using the following formula: , where q is a number of ADC bits.

L'error són zero per a Dc, petit a baixes freqüències, però significatiu quan les altes freqüències tenen amplituds altes. Aquest efecte es pot ignorar si s'inunda fora pel error que quantizing . Els requisits de nervi es poden comptar utilitzant la fórmula següent: , on q és un cert nombre de miques Adc.

| ADC resolution in bit |

input frequency | ||||||

|---|---|---|---|---|---|---|---|

| 1 Hz | 44.1 kHz | 192 kHz | 1 MHz | 10 MHz | 100 MHz | 1 GHz | |

| 8 | 1243 µs | 28.2 ns | 6.48 ns | 1.24 ns | 124 ps | 12.4 ps | 1.24 ps |

| 10 | 311 µs | 7.05 ns | 1.62 ns | 311 ps | 31.1 ps | 3.11 ps | 0.31 ps |

| 12 | 77.7 µs | 1.76 ns | 405 ps | 77.7 ps | 7.77 ps | 0.78 ps | 0.08 ps |

| 14 | 19.4 µs | 441 ps | 101 ps | 19.4 ps | 1.94 ps | 0.19 ps | 0.02 ps |

| 16 | 4.86 µs | 110 ps | 25.3 ps | 4.86 ps | 0.49 ps | 0.05 ps | – |

| 18 | 1.21 µs | 27.5 ps | 6.32 ps | 1.21 ps | 0.12 ps | – | – |

| 20 | 304 ns | 6.88 ps | 1.58 ps | 0.16 ps | – | – | – |

| 24 | 19.0 ns | 0.43 ps | 0.10 ps | – | – | – | – |

| 32 | 74.1 ps | – | – | – | – | – | – |

This table shows, for example, that it is not worth using a precise 24-bit ADC for sound recording if there is not an ultra low jitter clock. One should consider taking this phenomenon into account before choosing an ADC.

Aquesta taula mostra, per exemple, que no és valor utilitzar una 24 mica precisa Adc per a l'enregistrament de so si no hi ha un nervi ultrabaix rellotge. Un hauria de considerar tenir aquest fenomen en compte abans de triar un Adc.

Clock jitter is caused by phase noise.Error de citació: Es tanca el </ref> que manca per una etiqueta <ref>

[3]

The resolution of ADCs with a digitization bandwidth between 1 MHz and 1 GHz is limited by jitter.Error de citació: Es tanca el </ref> que manca per una etiqueta <ref>

When sampling audio signals at 44.1 kHz, the anti-aliasing filter should have eliminated all frequencies above 22 kHz.

Quan provant àudio fa senyals a 44.1 kHz, el filtre antialiasing hauria d'haver eliminat totes les freqüències damunt 22 kHz.

The input frequency (in this case, 22 kHz), not the ADC clock frequency, is the determining factor with respect to jitter performance.Error de citació: Es tanca el </ref> que manca per una etiqueta <ref>

Sampling rate

[modifica]The analog signal is continuous in time and it is necessary to convert this to a flow of digital values. It is therefore required to define the rate at which new digital values are sampled from the analog signal. The rate of new values is called the sampling rate or sampling frequency of the converter.

El senyal analògic és continu a temps i és necessari convertir això en un flux de valors digitals. S'exigeix per això que defineixi l'índex a què els valors digitals nous es proven des del senyal analògic. L'índex de valors nous s'anomena el índex de mostreig o freqüència de mostreig del convertidor.

A continuously varying bandlimited signal can be sampled (that is, the signal values at intervals of time T, the sampling time, are measured and stored) and then the original signal can be exactly reproduced from the discrete-time values by an interpolation formula. The accuracy is limited by quantization error. However, this faithful reproduction is only possible if the sampling rate is higher than twice the highest frequency of the signal. This is essentially what is embodied in the Shannon-Nyquist sampling theorem.

Un senyal de bandlimited contínuament variable es pot provar (allò és, els valors de senyal a intervals de temps T, el temps de mostreig, es mesuren i s'emmagatzemen) i llavors el senyal original pot ser exactament reproduït dels valors d'hora discreta per una fórmula d'interpolació. La precisió és limitada per l'error de quantització. Tanmateix, aquesta reproducció fidel és només possible si l'índex de mostreig és alt que dues vegades la freqüència més alta del senyal. Això és essencialment què està comprès en el Teorema de mostreig de shannon-nyquist.

Since a practical ADC cannot make an instantaneous conversion, the input value must necessarily be held constant during the time that the converter performs a conversion (called the conversion time). An input circuit called a sample and hold performs this task—in most cases by using a capacitor to store the analog voltage at the input, and using an electronic switch or gate to disconnect the capacitor from the input. Many ADC integrated circuits include the sample and hold subsystem internally.

Ja que un Adc pràctic no pot fer una conversió instantània, el valor d'entrada s'ha de mantenir necessàriament constant durant el temps que el convertidor realitzi una conversió (anomenat el temps de conversió ). Un circuit d'entrada anomenat una mostra i agafador funciona aquest tasca dins molts casos utilitzant un condensador per emmagatzemar el voltatge analògic a l'entrada, i utilitzant un canvi electrònic o porta per desconnectar el condensador de l'entrada. Molts Adc ELS circuits integrats inclouen el subsistema de mostra i agafador internament.

Aliasing

[modifica]All ADCs work by sampling their input at discrete intervals of time. Their output is therefore an incomplete picture of the behaviour of the input. There is no way of knowing, by looking at the output, what the input was doing between one sampling instant and the next. If the input is known to be changing slowly compared to the sampling rate, then it can be assumed that the value of the signal between two sample instants was somewhere between the two sampled values. If, however, the input signal is changing rapidly compared to the sample rate, then this assumption is not valid.

Tots els Adcs treballen per provar la seva entrada a intervals de temps discrets. La seva sortida és per això un quadre incomplet del comportament de l'entrada. No hi ha cap manera de saber, mirant la sortida, què estava fent l'entrada entre un instant de mostreig i el pròxim. Si se sap que l'entrada està canviant lentament comparat amb l'índex de mostreig, llavors es pot suposar que el valor del senyal entre dos instants de mostra era a algun lloc entre els dos valors provats. Si, tanmateix, el senyal d'entrada està canviant ràpidament comparat amb l'índex de mostra, llavors aquesta suposició no és vàlida.

If the digital values produced by the ADC are, at some later stage in the system, converted back to analog values by a digital to analog converter or DAC, it is desirable that the output of the DAC be a faithful representation of the original signal. If the input signal is changing much faster than the sample rate, then this will not be the case, and spurious signals called aliases will be produced at the output of the DAC. The frequency of the aliased signal is the difference between the signal frequency and the sampling rate. For example, a 2 kHz sine wave being sampled at 1.5 kHz would be reconstructed as a 500 Hz sine wave. This problem is called aliasing.

Si els valors digitals produïts per l'Adc són, en alguna etapa posterior en el sistema, es convertia altra vegada en valors analògics a prop un digital a convertidor analògic o Dac, és desitjable allò que la sortida del Dac és una representació fidel del senyal original. Si el senyal d'entrada està canviant molt més ràpid que l'índex de mostra, llavors això no serà el cas, i els senyals espuris anomenaven àlies serà produït a la sortida del Dac. La freqüència del senyal d'aliased és la diferència entre la freqüència de senyal i l'índex de mostreig. Per exemple, una ona de sinus de 2 kHz que es prova a 1.5 kHz es reconstruiria com a ona de sinus de 500 Hz. Aquest problema s'anomena aliasing .

To avoid aliasing, the input to an ADC must be low-pass filtered to remove frequencies above half the sampling rate. This filter is called an anti-aliasing filter, and is essential for a practical ADC system that is applied to analog signals with higher frequency content.

Per evitar aliasing, l'entrada a un Adc ha de ser pas baix filtrat per treure freqüències damunt la meitat de l'índex de mostreig. Aquest filtre es crida un antIaliasing filtre, i és essencial per a un sistema Adc pràctic que s'aplica a senyals analògics amb contingut de freqüència més alt.

Although aliasing in most systems is unwanted, it should also be noted that it can be exploited to provide simultaneous down-mixing of a band-limited high frequency signal (see undersampling and frequency mixer).

Encara que aliasing en la majoria dels sistemes és indesitjat, també un s'hauria de fixar que es pot explotar per proporcionar mescla de borrissol simultània d'un senyal d'alta freqüència limitat de banda (vegi undersampling i batedora de FREQÜÈNCIA).

Dither

[modifica]In A-to-D converters, performance can usually be improved using dither. This is a very small amount of random noise (white noise) which is added to the input before conversion. Its amplitude is set to be twice the value of the least significant bit. Its effect is to cause the state of the LSB to randomly oscillate between 0 and 1 in the presence of very low levels of input, rather than sticking at a fixed value. Rather than the signal simply getting cut off altogether at this low level (which is only being quantized to a resolution of 1 bit), it extends the effective range of signals that the A-to-D converter can convert, at the expense of a slight increase in noise - effectively the quantization error is diffused across a series of noise values which is far less objectionable than a hard cutoff. The result is an accurate representation of the signal over time. A suitable filter at the output of the system can thus recover this small signal variation.

En convertidors d'A-to-D, l'actuació es pot normalment millorar utilitzant dither. Això és una quantitat molt petita de soroll fortuït (soroll blanc) que s'afegeix a l'entrada abans de conversió. La seva amplitud es posa per ser dues vegades el valor del bit de mínima significació. El seu efecte és provocar l'estat del Lsb per oscil·lar fortuïtament 0 i 1 en la presència de molt baixos nivells d'entrada, més que persistint en un valor fix. Més aviat que el senyal que simplement es talla conjuntament en aquest baix nivell (que s'està quantized només a una resolució d'1 mica), estén l'abast efectiu de senyals que el convertidor d'A-to-D es pot convertir, a compte d'un augment lleuger en soroll - eficaçment l'error de quantització es difon a l'altre costat d'una sèrie de valors de soroll que és molt menys objectionable que un obturador dur. El resultat és una representació acurada del senyal gradualment. Un filtre adequat a la sortida del sistema pot així recobrar aquesta variació de senyal petita.

An audio signal of very low level (with respect to the bit depth of the ADC) sampled without dither sounds extremely distorted and unpleasant. Without dither the low level may cause the least significant bit to "stick" at 0 or 1. With dithering, the true level of the audio may be calculated by averaging the actual quantized sample with a series of other samples [the dither] that are recorded over time.

Un senyal d'àudio de molt baix nivell (respecte a la profunditat de mica de l'Adc) provat sense dither sons extremadament distorsionats i desagradables. Sense dither el baix nivell pot fer el bit de mínima significació per "persistir" en les 0 o 1. Amb dithering, el nivell veritable de l'àudio es pot comptar fent una mitjana de la mostra quantized real amb una sèrie d'unes altres mostres [el dither] que són enregistrats gradualment.

A virtually identical process, also called dither or dithering, is often used when quantizing photographic images to a fewer number of bits per pixel—the image becomes noisier but to the eye looks far more realistic than the quantized image, which otherwise becomes banded. This analogous process may help to visualize the effect of dither on an analogue audio signal that is converted to digital.

Un procés virtualment idèntic, també anomenava dither o dithering, és sovint utilitzat en quantizing imatges fotogràfiques a un menys número de miques per imatge píxel el converteix més sorollós però als aspectes d'ull molt més realistes que la imatge quantized, que altrament es torna embolcada. Aquest procés anàleg pot ajudar a visualitzar l'efecte de dither en un senyal d'àudio anàleg que es converteix en digital.

Dithering is also used in integrating systems such as electricity meters. Since the values are added together, the dithering produces results that are more exact than the LSB of the analog-to-digital converter.

Dithering també s'utilitza integrant sistemes com comptadors elèctrics. Ja que els valors s'afegeixen junts, el dithering produeix resultats que són més exactes que el Lsb del convertidor analògic/digital.

Note that dither can only increase the resolution of a sampler, it cannot improve the linearity, and thus accuracy does not necessarily improve.

Nota que dither només pot augmentar la resolució d'un mostrejador, no pot millorar el linearity, i així la precisió no millora necessàriament.

Oversampling

[modifica]Usually, signals are sampled at the minimum rate required, for economy, with the result that the quantization noise introduced is white noise spread over the whole pass band of the converter. If a signal is sampled at a rate much higher than the Nyquist frequency and then digitally filtered to limit it to the signal bandwidth there are the following advantages:

Normalment, els senyals es proven com a mínim índex exigit, per a l'economia, amb el resultat que el soroll de quantització introduït és soroll blanc estès sobre la banda de pas sencera del convertidor. Si un senyal es prova a un índex molt més alt que la Freqüència de nyquist i llavors digitalment es FILTRA per limitar-lo a l'amplada de banda de senyal hi ha els avantatges següents:

- digital filters can have better properties (sharper rolloff, phase) than analogue filters, so a sharper anti-aliasing filter can be realised and then the signal can be downsampled giving a better result

- els filtres digitals poden tenir millors propietats (rolloff afilat, fase) que els filtres anàlegs, així un es pot adonar d'un filtre antialiasing més agut i llavors el senyal pot ser downsampled que dóna un millor resultat

- a 20-bit ADC can be made to act as a 24-bit ADC with 256× oversampling

- una 20 mica Adc es pot fer servir com a 24 mica Adc amb 256× sobreprovant

- the signal-to-noise ratio due to quantization noise will be higher than if the whole available band had been used. With this technique, it is possible to obtain an effective resolution larger than that provided by the converter alone

- la proporció de signal-to-noise a causa de soroll de quantització serà més alta que no si la banda disponible sencera s'havia utilitzat. Amb aquesta tècnica, és possible obtenir una resolució eficaç més gran que allò proporcionada pel convertidor de manera sola

- The improvement in SNR is 3 dB (equivalent to 0.5 bits) per octave of oversampling which is not sufficient for many applications. Therefore, oversampling is usually coupled with noise shaping (see sigma-delta modulators). With noise shaping, the improvement is 6L+3 dB per octave where L is the order of loop filter used for noise shaping. e.g. - a 2nd order loop filter will provide an improvement of 15 dB/octave.

- La millora a Snr és 3 dB (equivalent a 0.5 miques) per octava de sobreprovar que no és suficient per gaires aplicacions. Per això, sobreprovant és normalment associat amb formació de soroll (vegi moduladors de sigma-delta). Amb formació de soroll, la millora és 6L+3 dB per octava on L és l'ordre de filtre de bucle utilitzat per a la formació de soroll. p. ex. - un 2n filtre de bucle d'ordre proporcionarà una millora de 15 dB/octave.

Relative speed and precision

[modifica]The speed of an ADC varies by type. The Wilkinson ADC is limited by the clock rate which is processable by current digital circuits. Currently, frequencies up to 300 MHz are possible. The conversion time is directly proportional to the number of channels. For a successive approximation ADC, the conversion time scales with the logarithm of the number of channels. Thus for a large number of channels, it is possible that the successive approximation ADC is faster than the Wilkinson. However, the time consuming steps in the Wilkinson are digital, while those in the successive approximation are analog. Since analog is inherently slower than digital, as the number of channels increases, the time required also increases. Thus there are competing processes at work. Flash ADCs are certainly the fastest type of the three. The conversion is basically performed in a single parallel step. For an 8-bit unit, conversion takes place in a few tens of nanoseconds.

La velocitat d'un Adc varia per tipus. El Wilkinson Adc és limitat per l'índex de rellotges que és processable per circuits integrats digitals actuals. Actualment, les freqüències fins a 300 Mhz són possibles. El temps de conversió és directament proporcional al número de canals. Per a una successiva aproximació Adc, les escales d'hora de conversió amb el logaritme del número de canals. Així per a un número gran de canals, és possible que la successiva aproximació Adc sigui més ràpida que el Wilkinson. Tanmateix, el temps que consumeix els passos al Wilkinson són digitals, mentre que aquells en la successiva aproximació són analògics. Des d'ordinador analògic és inherentment més lent que digital, mentre el número de canals augmenta, el temps exigit també augmenta. Així allà són processos que competeixen a la feina. Flaix que Adcs són naturalment el tipus més ràpid dels tres. La conversió es realitza bàsicament en un pas paral·lel únic. Per a una unitat de 8 mica, la conversió té lloc en uns quants tens de nanosegons.

There is, as expected, somewhat of a trade off between speed and precision. Flash ADCs have drifts and uncertainties associated with the comparator levels, which lead to poor uniformity in channel width. Flash ADCs have a resulting poor linearity. For successive approximation ADCs, poor linearity is also apparent, but less so than for flash ADCs. Here, non-linearity arises from accumulating errors from the subtraction processes. Wilkinson ADCs are the best of the three. These have the best differential non-linearity. The other types require channel smoothing in order to achieve the level of the Wilkinson.[4][5]

Hi ha, com esperat, una mica d'un comerç d'entre velocitat i precisió. El flaix que Adcs tenen va a la deriva i les incerteses s'associaven amb els nivells de comparadors, que condueixen a uniformitat pobra en amplada de canal. Flaix que Adcs tenen un linearity pobre que resulta. Per a la successiva aproximació Adcs, linearity pobre és també aparent, però menys així que pel flaix Adcs. Aquí, no-linearity sorgeix d'errors que s'acumulen dels processos de sostracció. Wilkinson Adcs són el millor dels tres. Aquests tenen el millor no-linearity diferencial. Els altres tipus exigeixen poliment de canal per aconseguir el nivell del Wilkinson.[6][7].

The sliding scale principle

[modifica]The sliding scale or randomizing method can be employed to greatly improve the channel width uniformity and differential linearity of any type of ADC, but especially flash and successive approximation ADCs. Under normal conditions, a pulse of a particular amplitude is always converted to a certain channel number. The problem lies in that channels are not always of uniform width, and the differential linearity decreases proportionally with the divergence from the average width. The sliding scale principle uses an averaging effect to overcome this phenomenon. A random, but known analog voltage is added to the input pulse. It is then converted to digital form, and the equivalent digital version is subtracted, thus restoring it to its original value. The advantage is that the conversion has taken place at a random point. The statistical distribution of the final channel numbers is decided by a weighted average over a region of the range of the ADC. This in turn desensitizes it to the width of any given channel.[8][9]

L'escala corredissa o mètode que randomizing es poden emprar per millorar en gran manera la uniformitat d'amplada de canal i linearity diferencial de qualsevol tipus d'Adc, però especialment flaix i la successiva aproximació Adcs. Sota condicions normals, un pols d'una amplitud particular sempre es converteix en un cert número de canal. El problema és ja que els canals no són sempre d'amplada uniforme, i el linearity diferencial disminueix proporcionalment amb la divergència de l'amplada mitjana. El principi d'escala corredís utilitza un efecte que fa una mitjana per vèncer aquest fenomen. Un voltatge analògic fortuït, però conegut s'afegeix al pols d'entrada. Es converteix llavors en forma digital, i la versió digital equivalent es resta, així tornant-lo al seu valor original. L'avantatge és que la conversió ha tingut lloc en un punt fortuït. La distribució estadística dels números de canal finals és decidida per una mitjana carregada sobre una regió de la gamma de l'Adc. Això a canvi l'insensibilitza a l'amplada de qualsevol canal donat.[10][11].

ADC structures

[modifica]These are the most common ways of implementing an electronic ADC:

Aquestes són les maneres més comunes d'implementar un Adc electrònic:

- A direct conversion ADC or flash ADC has a bank of comparators sampling the input signal in parallel, each firing for their decoded voltage range. The comparator bank feeds a logic circuit that generates a code for each voltage range. Direct conversion is very fast, capable of gigahertz sampling rates, but usually has only 8 bits of resolution or fewer, since the number of comparators needed, 2N - 1, doubles with each additional bit, requiring a large expensive circuit. ADCs of this type have a large die size, a high input capacitance, high power dissipation, and are prone to produce glitches on the output (by outputting an out-of-sequence code). Scaling to newer submicrometre technologies does not help as the device mismatch is the dominant design limitation. They are often used for video, wideband communications or other fast signals in optical storage.

- Un conversió directa Adc o Flash adc té un banc de comparadors que proven el senyal d'entrada en paral·lel, cada tiroteig per a la seva gamma de voltatge descodificada. El banc de comparadors alimenta un circuit integrat lògic que genera un codi per a cada voltatge amb gamma. La conversió directa és molt ràpida, capaç de gigahertz el mostreig considera, però normalment té només 8 miques de resolució o menys, des del número de comparadors necessitats, 2N - 1, dobles amb cada mica addicional, que exigeix un circuit car gran. Els Adcs d'aquest tipus tenen un gran morir mida, una capacitància d'entrada alta, dissipació de poder alta, i són propensos a produir problemes tècnics a la sortida (imprimint un codi fora de seqüència). Reduint a submicròmetre més nou tecnologies fa no ajudar com el malpartit de mecanismes és la limitació de disseny dominant. S'utilitzen sovint per a video, comunicacions de wideband o uns altres senyals ràpids en emmagatzematge òptic.

- A successive-approximation ADC uses a comparator to reject ranges of voltages, eventually settling on a final voltage range. Successive approximation works by constantly comparing the input voltage to the output of an internal digital to analog converter (DAC, fed by the current value of the approximation) until the best approximation is achieved. At each step in this process, a binary value of the approximation is stored in a successive approximation register (SAR). The SAR uses a reference voltage (which is the largest signal the ADC is to convert) for comparisons. For example if the input voltage is 60 V and the reference voltage is 100 V, in the 1st clock cycle, 60 V is compared to 50 V (the reference, divided by two. This is the voltage at the output of the internal DAC when the input is a '1' followed by zeros), and the voltage from the comparator is positive (or '1') (because 60 V is greater than 50 V). At this point the first binary digit (MSB) is set to a '1'. In the 2nd clock cycle the input voltage is compared to 75 V (being halfway between 100 and 50 V: This is the output of the internal DAC when its input is '11' followed by zeros) because 60 V is less than 75 V, the comparator output is now negative (or '0'). The second binary digit is therefore set to a '0'. In the 3rd clock cycle, the input voltage is compared with 62.5 V (halfway between 50 V and 75 V: This is the output of the internal DAC when its input is '101' followed by zeros). The output of the comparator is negative or '0' (because 60 V is less than 62.5 V) so the third binary digit is set to a 0. The fourth clock cycle similarly results in the fourth digit being a '1' (60 V is greater than 56.25 V, the DAC output for '1001' followed by zeros). The result of this would be in the binary form 1001. This is also called bit-weighting conversion, and is similar to a binary search. The analogue value is rounded to the nearest binary value below, meaning this converter type is mid-rise (see above). Because the approximations are successive (not simultaneous), the conversion takes one clock-cycle for each bit of resolution desired. The clock frequency must be equal to the sampling frequency multiplied by the number of bits of resolution desired. For example, to sample audio at 44.1 kHz with 32 bit resolution, a clock frequency of over 1.4 MHz would be required. ADCs of this type have good resolutions and quite wide ranges. They are more complex than some other designs.

- uN '''successive-approximation Adc usos un comparador per rebutjar gammes de voltatges, finalment instal·lant-se en una gamma de voltatge final. La successiva aproximació funciona per constantment comparar el voltatge d'entrada amb la sortida d'un intern digital a convertidor analògic (Dac, alimentat pel valor actual de l'aproximació) fins a la millor aproximació és aconseguit. En cada pas en aquest procés, un valor binari de l'aproximació s'emmagatzema en un successiu registre d'aproximació (Sar). El Sar utilitza un voltatge de referència (que és el senyal més gran que l'Adc hagi de convertir) per a comparacions. Per exemple si el voltatge d'entrada són 60 V i el voltatge de referència són 100 V, durant el 1r cicle de rellotges, 60 V és comparat a 50 V (la referència, dividida per les dues. Això és el voltatge a la sortida del Dac intern quan l'entrada és una '1' seguida per posa a zero), i el voltatge des del comparador és positiu (o '1) (perquè 60 V és més gran que 50 V). En aquest punt la primera xifra binària (MSB) es posa a un '1'. Durant el 2n cicle de rellotges el voltatge d'entrada es compara amb 75 V (sent intermedi entre 100 i 50 V: Això és la sortida del Dac intern quan la seva entrada són '11' seguits per posa a zero) perquè 60 V és menys de 75 V, la sortida de comparadors és ara negativa (o '0). La segona xifra binària és per això conjunt a un '0'. Durant el 3r cicle de rellotges, el voltatge d'entrada es compara amb 62.5 V (a mig camí entre 50 V i 75 V: Això és la sortida del Dac intern quan la seva entrada són '101' seguits per posa a zero). La sortida del comparador és negativa o '0' (perquè 60 V és menys de 62.5 V) així la tercera xifra binària és posada a un 0. El quart cicle de rellotges similarment ocasiona el quart dígit que és un '1' (60 V és més gran que 56.25 V, el Dac imprimia perquè '1001' seguia a prop posa a zero). El resultat d'això seria en la forma 1001 binària. Això també es crida conversió de pes estadístic de mica, i és similar a una cerca binària. El valor anàleg s'arrodoneix al valor més a prop binari sota, significant que aquest tipus de convertidor sigui mig pujada (vegi-hi més amunt). Perquè les aproximacions són successiu (no simultani), la conversió en pren un anar amb bicicleta als rellotges per a cada mica de resolució desitjada. La freqüència de rellotges ha de ser igual a la freqüència de mostreig multiplicada pel número de miques de resolució desitjada. Per exemple, provar àudio a 44.1 kHz amb 32 resolució de mica, una freqüència de rellotges de sobre 1.4 Mhz seria demanat. Els Adcs d'aquest tipus tenen bones resolucions i gammes bastant àmplies. Són més complexos que alguns altres dissenys.

- A ramp-compare ADC produces a saw-tooth signal that ramps up or down then quickly returns to zero. When the ramp starts, a timer starts counting. When the ramp voltage matches the input, a comparator fires, and the timer's value is recorded. Timed ramp converters require the least number of transistors. The ramp time is sensitive to temperature because the circuit generating the ramp is often just some simple oscillator. There are two solutions: use a clocked counter driving a DAC and then use the comparator to preserve the counter's value, or calibrate the timed ramp. A special advantage of the ramp-compare system is that comparing a second signal just requires another comparator, and another register to store the voltage value. A very simple (non-linear) ramp-converter can be implemented with a microcontroller and one resistor and capacitor.[12] Vice versa, a filled capacitor can be taken from an integrator, time-to-amplitude converter, phase detector, sample and hold circuit, or peak and hold circuit and discharged. This has the advantage that a slow comparator cannot be disturbed by fast input changes.

- Un és comparable a la rampa Adc produeix un senyal de dent de serra allò rampes amunt o avall llavors de pressa retorns a zero. Quan la rampa comença, comença a comptar un temporitzador. Quan el voltatge de rampa lliga amb l'entrada, dispara un comparador, i el valor del temporitzador s'enregistra. Els convertidors de rampa cronometrats exigeixen el número més menor de transistors. El temps de rampa és sensible a temperatura perquè que el circuit generi la rampa és sovint just algun oscil·lador simple. Hi ha dues solucions: utilitzi una contraconducció registrada un Dac i llavors utilitzi el comparador per conservar el valor del taulell, o calibrar la rampa cronometrada. Un avantatge especial del comparar rampa sistema és que sent comparable un segon senyal només exigeix un altre comparador, i un altre registre per emmagatzemar el valor de voltatge. Un convertidor de rampa molt simple (no lineal) es pot implementar amb un microcontrolador i un resistor i condensador.[13]Viceversa, un condensador omplert es pot prendre d'un integrador|INTEGRADOR, convertidor hora a amplitud, detector de fase, circuit de MOSTRA I AGAFADOR, o CIM I circuit d'AGAFADOR i desembocava. Això té ràpid l'avantatge pel qual un comparador lent no pot ser molestat canvis d'entrada.

- The Wilkinson ADC was designed by D. H. Wilkinson in 1950. The Wilkinson ADC is based on the comparison of an input voltage with that produced by a charging capacitor. The capacitor is allowed to charge until its voltage is equal to the amplitude of the input pulse. (A comparator determines when this condition has been reached.) Then, the capacitor is allowed to discharge linearly, which produces a ramp voltage. At the point when the capacitor begins to discharge, a gate pulse is initiated. The gate pulse remains on until the capacitor is completely discharged. Thus the duration of the gate pulse is directly proportional to the amplitude of the input pulse. This gate pulse operates a linear gate which receives pulses from a high-frequency oscillator clock. While the gate is open, a discrete number of clock pulses pass through the linear gate and are counted by the address register. The time the linear gate is open is proportional to the amplitude of the input pulse, thus the number of clock pulses recorded in the address register is proportional also. Alternatively, the charging of the capacitor could be monitored, rather than the discharge.[14][15]

- El Wilkinson Adc estava dissenyat per D. H. Wilkinson el 1950. Basa el Wilkinson Adc en la comparació d'un voltatge d'entrada amb allò produïda un condensador de càrrega. El condensador es deixa carregar fins que el seu voltatge sigui igual a l'amplitud del pols d'entrada. (Un comparador determina quan s'ha arribat a aquesta condició.) Llavors, el condensador es deixa desembocar linealment, la qual cosa produeix un voltatge de rampa. En el punt quan el condensador comença a desembocar, un pols de porta s'inicia. El pols de porta roman damunt fins que el condensador es descarregui completament. Així la duració del pols de porta és directament proporcional a l'amplitud del pols d'entrada. Aquest pols de porta fa servir una porta lineal que rep polsos d'un rellotge d'oscil·ladors de freqüència alta. Mentre que la porta és oberta, un número discret de senyals de rellotge passen a través de la porta lineal i es compten pel registre d'adreça. El temps que la porta lineal és oberta és proporcional a l'amplitud del pols d'entrada, així el número de senyals de rellotge enregistrats en el registre d'adreça és proporcional també. Alternativament, la càrrega del condensador es podria controlar, més que la descàrrega.[16][17].

- An integrating ADC (also dual-slope or multi-slope ADC) applies the unknown input voltage to the input of an integrator and allows the voltage to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution. Converters of this type (or variations on the concept) are used in most digital voltmeters for their linearity and flexibility.

- uN '''integrating ADC (també pendent de dual o multipendent Adc) aplica el voltatge d'entrada desconegut a l'entrada d'un integrador|INTEGRADOR i permet el voltatge a rampa per un període d'hora fix (el període de correguda d'impuls). Llavors un voltatge de referència conegut de davant polaritat és aplicat a l'integrador i és permès a rampa fins que la sortida d'integrador retorni a zero (el període cursa avall). El voltatge d'entrada es computa com a funció del voltatge de referència, el període d'hora de correguda d'impuls constant, i el període d'hora cursa avall mesurat. La mesura d'hora cursa avall es fa normalment en unitats del rellotge del convertidor, els temps d'integració tan llargs tenen en compte resolucions més altes. De la mateixa manera, la velocitat del convertidor es pot millorar sacrificant resolució. Els convertidors d'aquest tipus (o variacions sobre el concepte) s'utilitzen en la majoria dels Voltímetres de voltmeter#digital|voltímetres digitals|VOLTÍMETRES per al seu linearity i flexibilitat.

- A delta-encoded ADC or Counter-ramp has an up-down counter that feeds a digital to analog converter (DAC). The input signal and the DAC both go to a comparator. The comparator controls the counter. The circuit uses negative feedback from the comparator to adjust the counter until the DAC's output is close enough to the input signal. The number is read from the counter. Delta converters have very wide ranges, and high resolution, but the conversion time is dependent on the input signal level, though it will always have a guaranteed worst-case. Delta converters are often very good choices to read real-world signals. Most signals from physical systems do not change abruptly. Some converters combine the delta and successive approximation approaches; this works especially well when high frequencies are known to be small in magnitude.

- Un Adc codificat de delta o contrarampa té un taulell amunt avall que s'alimenta un digital a convertidor analògic (Dac). El senyal d'entrada i el Dac se'n van els dos a un comparador. El comparador controla el taulell. El circuit utilitza resposta negativa des del comparador per ajustar el taulell fins que la sortida del Dac sigui prou propera fins al senyal d'entrada. El número es llegeix des del taulell. Els convertidors de delta tenen gammes molt àmplies, i resolució alta, però el temps de conversió és dependent del nivell de senyal d'entrada, encara que sempre tindrà un pitjor cas garantit. Els convertidors de delta són sovint molt bones eleccions a senyals de món real marcats. Molts senyals des de sistemes físics no canvien abruptament. Alguns convertidors combinen el delta i la successiva aproximació s'acosta; això funciona especialment bé quan se sap que les altes freqüències són petites en magnitud.

- A pipeline ADC (also called subranging quantizer) uses two or more steps of subranging. First, a coarse conversion is done. In a second step, the difference to the input signal is determined with a digital to analog converter (DAC). This difference is then converted finer, and the results are combined in a last step. This can be considered a refinement of the successive approximation ADC wherein the feedback reference signal consists of the interim conversion of a whole range of bits (for example, four bits) rather than just the next-most-significant bit. By combining the merits of the successive approximation and flash ADCs this type is fast, has a high resolution, and only requires a small die size.

- Un canonada Adc (també anomenat quantizer que se subestén) usos dos o més passos de subestendre's. Primer, es fa una conversió tosca. En un segon pas, la diferència al senyal d'entrada està determinada amb un digital a convertidor analògic (Dac). Aquesta diferència es converteix llavors més fi, i els resultats es combinen en un últim pas. Això es pot considerar un refinament de la successiva aproximació Adc on consta el senyal de referència de resposta de la conversió interina d'una gamma sencera de miques (per exemple, quatre miques) força que només la mica després-més-significativa. Combinant els mèrits de la successiva aproximació i el flaix Adcs aquest tipus és ràpid, té una resolució alta, i només exigeix un petit morir mida.

- A Sigma-Delta ADC (also known as a Delta-Sigma ADC) oversamples the desired signal by a large factor and filters the desired signal band. Generally, a smaller number of bits than required are converted using a Flash ADC after the filter. The resulting signal, along with the error generated by the discrete levels of the Flash, is fed back and subtracted from the input to the filter. This negative feedback has the effect of noise shaping the error due to the Flash so that it does not appear in the desired signal frequencies. A digital filter (decimation filter) follows the ADC which reduces the sampling rate, filters off unwanted noise signal and increases the resolution of the output (sigma-delta modulation, also called delta-sigma modulation).

- Un Sigma-Delta Adc (també conegut com un Delta-Sigma Adc) oversamples el senyal desitjat per un factor gran i filtres la banda de senyal desitjada. Generalment, un número més petit de miques que exigit són convertits utilitzant un Flaix Adc després del filtre. El senyal que resulta, junt amb l'error generat pels nivells discrets del Flaix, s'alimenta altra vegada i es resta de l'entrada al filtre. Aquesta resposta negativa té l'efecte de soroll que forma l'error a causa del Flaix de manera que no aparegui en les freqüències de senyal desitjades. Un filtre digital (filtre de decimation) segueix l'Adc que redueix l'índex de mostreig, es filtra de senyal de soroll indesitjat i augmenta la resolució de la sortida (sigma-delta modulation, també anomenat MODULACIÓ de SIGMA de DELTA).

- A Time-interleaved ADC uses M parallel ADCs where each ADC sample data every M:th cycle of the effective sample clock. The result is that the sample rate is increased M times compared to what each individual ADC can manage. In practice, the individual differences between the M ADCs degrade the overall performance reducing the SFDR. However, technologies exist to correct for these time-interleaving mismatch errors.

- Un Adc interleaved d'Hora paral·lela M d'usos Adcs on cada dades de mostra Adc tots els cicles de M:th del rellotge de mostra eficaç. El resultat és que l'índex de mostra s'augmenta temps M comparats amb el que cada individu Adc pot gestionar. En la pràctica, les diferències individuals entre el M Adcs degraden l'actuació global que redueix el Sfdr. Tanmateix, les tecnologies existeixen per corregir per a aquests errors malpartit que interleaving hora.

- An ADC with intermediate FM stage first uses a voltage-to-frequency converter to converts the desired signal into an oscillating signal with a frequency proportional to the voltage of the desired signal, and then uses a frequency counter to convert that frequency into a digital count proportional to the desired signal voltage. Longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution. The two parts of the ADC may be widely separated, with the frequency signal passed through a opto-isolator or transmitted wirelessly. Some such ADCs use sine wave or square wave frequency modulation; others use pulse-frequency modulation. Such ADCs were once the most popular way to show a digital display of the status of a remote analog sensor.Error de citació: Es tanca el

</ref>que manca per una etiqueta<ref>Error de citació: Etiqueta<ref>no vàlida;

les referències sense nom han de tenir contingut[18]Error de citació: Etiqueta <ref> no vàlida;

les referències sense nom han de tenir contingut[19]Error de citació: Etiqueta <ref> no vàlida;

les referències sense nom han de tenir contingut[20]Error de citació: Etiqueta <ref> no vàlida;

les referències sense nom han de tenir contingut[21]

</Ref>.

There can be other ADCs that use a combination of electronics and other technologies:

Hi pot haver un altre Adcs que utilitzen una combinació d'electrònica i unes altres tecnologies:

- A Time-stretch analog-to-digital converter (TS-ADC) digitizes a very wide bandwidth analog signal, that cannot be digitized by a conventional electronic ADC, by time-stretching the signal prior to digitization. It commonly uses a photonic preprocessor frontend to time-stretch the signal, which effectively slows the signal down in time and compresses its bandwidth. As a result, an electronic backend ADC, that would have been too slow to capture the original signal, can now capture this slowed down signal. For continuous capture of the signal, the frontend also divides the signal into multiple segments in addition to time-stretching. Each segment is individually digitized by a separate electronic ADC. Finally, a digital signal processor rearranges the samples and removes any distortions added by the frontend to yield the binary data that is the digital representation of the original analog signal.

- uN '''time-stretch analog-to-digital converter (ts-adc) digitalitza una amplada de banda molt ampla senyal d'ordinador analògic, que no pot ser digitalitzat per un Adc electrònic convencional, per estirament d'hora el senyal abans de digitalització. Comunament utilitza un PREPROCESSOR frontend fotònic a elàstic d'hora el senyal, que eficaçment alenteix el senyal a temps i comprimeix la seva amplada de banda. Com a resultat, un backend Adc electrònic, allò hauria estat massa lent per captar el senyal original, pot ara captar això alentit senyal. Per a la captura contínua del senyal, el frontend també divideix el senyal en segments múltiples a més a més a estirament d'hora. Cada segment és individualment digitalitzat per un Adc electrònic separat. Finalment, un processador de senyal digital canvia les mostres i treu algunes distorsions afegides pel frontend per produir les dades binàries que són la representació digital del senyal analògic original.

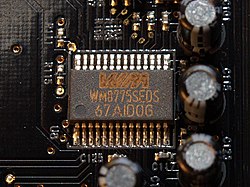

Commercial analog-to-digital converters

[modifica]These are usually integrated circuits.

Aquests S'integren normalment CIRCUITS.

Most converters sample with 6 to 24 bits of resolution, and produce fewer than 1 megasample per second. Thermal noise generated by passive components such as resistors masks the measurement when higher resolution is desired. For audio applications and in room temperatures, such noise is usually a little less than 1 μV (microvolt) of white noise. If the Most Significant Bit corresponds to a standard 2 volts of output signal, this translates to a noise-limited performance that is less than 20~21 bits, and obviates the need for any dithering. Mega- and gigasample per second converters are available, though (Feb 2002). Megasample converters are required in digital video cameras, video capture cards, and TV tuner cards to convert full-speed analog video to digital video files.

La majoria dels convertidors proven amb 6 a 24 miques de resolució, i en produeixen menys que 1 megamostra per segon. El Soroll tèrmic generat per components passius com resistors emmascara la mesura quan resolució més alta és desitjat. Per a aplicacions d'àudio i en temperatures ambientals, tal soroll és normalment una mica menys d'1 μV (microvolt) de soroll blanc. Si el Bit de Més Significació correspon a un estàndard 2 volts de sortida fan senyals, això es tradueix a una actuació limitada de soroll que és menys que les miques de 20~21, i obvia la necessitat de qualsevol dithering. Mega- i gigamostra per segons convertidors estan disponibles, tanmateix (febr. de 2002). Els convertidors Megasample s'exigeixen en càmeres de vídeo digitals, la captura de vídeo Carda, i les TARGETES D'AFINADOR DE TV per convertir ordinador analògic de velocitat plena graven a arxius de vídeo digitals. Commercial converters usually have ±0.5 to ±1.5 LSB error in their output.

Els convertidors comercials normalment tenen ±0.5 a error de ±1.5 Lsb a la seva sortida.

In many cases the most expensive part of an integrated circuit is the pins, because they make the package larger, and each pin has to be connected to the integrated circuit's silicon. To save pins, it is common for slow ADCs to send their data one bit at a time over a serial interface to the computer, with the next bit coming out when a clock signal changes state, say from zero to 5 V. This saves quite a few pins on the ADC package, and in many cases, does not make the overall design any more complex (even microprocessors which use memory-mapped I/O only need a few bits of a port to implement a serial bus to an ADC).

En molts casos la part més cara d'un circuit integrat és les agulles, perquè fan més gran el paquet, i cada agulla ha de ser connectada al silici del circuit integrat. Per guardar agulles, és comú que Adcs lent enviï una mica alhora a les seves dades sobre una interfície en Sèrie a l'ordinador, amb la pròxima mica que es descobreix quan canvia un senyal de rellotges estat, dir des de les zero a 5 V. Això estalvia bastants agulles en el paquet Adc, i en gaires casos, no fa el disseny global ja complex (fins i tot els microprocessadors que utilitzen MEMORY-MAPPED I/O només necessiten unes quantes miques d'un port per implementar un autobús en sèrie a un Adc).

Commercial ADCs often have several inputs that feed the same converter, usually through an analog multiplexer. Different models of ADC may include sample and hold circuits, instrumentation amplifiers or differential inputs, where the quantity measured is the difference between two voltages.

Els Adcs comercials sovint tenen unes quantes entrades que alimenten el mateix convertidor, normalment a través d'un multiplexor analògic. Els models diferents d'Adc poden incloure circuits de mostra i agafador, amplificadors d'instrumentació o entrades diferencials, on la quantitat mesurada és la diferència entre dos voltatges.

Applications

[modifica]Application to music recording

[modifica]ADCs are integral to current music reproduction technology. Since much music production is done on computers, when an analog recording is used, an ADC is needed to create the PCM data stream that goes onto a compact disc or digital music file.

Els Adcs són integrals a tecnologia de reproducció de música actual. Ja que molta producció de música es fa en ordinadors, quan s'utilitza un enregistrament analògic, un Adc es necessita per crear el corrent de dades de Pcm que se'n va a un disc compacte o arxiu de música digital.

The current crop of AD converters utilized in music can sample at rates up to 192 kilohertz. High bandwidth headroom allows the use of cheaper or faster anti-aliasing filters of less severe filtering slopes. The proponents of oversampling assert that such shallower anti-aliasing filters produce less deleterious effects on sound quality, exactly because of their gentler slopes. Others prefer entirely filterless AD conversion, arguing that aliasing is less detrimental to sound perception than pre-conversion brickwall filtering. Considerable literature exists on these matters, but commercial considerations often play a significant role. Most high-profile recording studios record in 24-bit/192-176.4 kHz PCM or in DSD formats, and then downsample or decimate the signal for Red-Book CD production (44.1 kHz or at 48 kHz for commonly used for radio/TV broadcast applications).

La collita actual de convertidors d'Anunci utilitzats en la música pot provar a índexs fins 192 kilohertzs. L'amplada de banda alta que headroom deixa l'ús de filtres antIaliasing més barats o més ràpids de menys filtratge sever s'inclina. Els defensors de sobreprovar afirmen que tals filtres antialiasing de shallower produeixen menys efectes nocius sobre qualitat sòlida, exactament a causa dels seus pendents més suaus. Altres prefereixen conversió d'Anunci totalment filterless, sostenint que aliasing és menys perjudicial per fer sonar percepció que filtrant-se brickwall preconversió. La literatura considerable existeix en aquestes matèries, però les consideracions comercials sovint juguen un paper significatiu. Citació de Most registre d'estudis de gravació de perfil alt en 24-bit/192-176.4 kHz Pcm o en formats de Dsd, i llavors downsample o delma el senyal per a la producció de cd de Llibre Vermell (44.1 kHz o a 48 kHz per comunament utilitzat per a ràdio/Tv aplicacions d'emissió).

Digital Signal Processing

[modifica]AD converters are used virtually everywhere where an analog signal has to be processed, stored, or transported in digital form. Fast video ADCs are used, for example, in TV tuner cards. Slow on-chip 8, 10, 12, or 16 bit ADCs are common in microcontrollers. Very fast ADCs are needed in digital oscilloscopes, and are crucial for new applications like software defined radio.

Els convertidors d'anunci s'utilitzen virtualment a tot arreu on s'ha de processar un senyal analògic, emmagatzemar-se, o transportar-se a forma digital. Vídeo ràpid Adcs són utilitzats, per exemple, en Targetes d'afinador de TV. El damunt tros 8 lent, la mica de 10, 12, o 16 Adcs són comuns en microcontroladors. Els Adcs molt ràpids es necessiten a L'Oscil·loscopi d'emmagatzematge de oscilloscope#digital|oscil·loscopis digitals|oscil·loscopis digitals, i són crucials perquè les aplicacions noves com PROGRAMARI DEFINIEN RÀDIO.

Electrical Symbol

[modifica]Veure també

[modifica]- quantització (processament de SENYAL)

- Modem

- amplificador de SAMPLE-AND-HOLD

- Ideal sampler

Referencies

[modifica]- ↑ although analog-to-digital conversion is an inherently non-linear process (since the mapping of a continuous space to a discrete space is a piecewise-constant and therefore non-linear operation).

- ↑ lineal. encara que la conversió d'analog-to-digital és un procés inherentment no lineal (ja que el mapatge d'un espai continu a un espai discret és un constant de piecewise i per això operació no lineal).

- ↑ . "Jitter effects on Analog to Digital and Digital to Analog Converters" Que "el nervi efectua sobre Ordinador Analògic a Digital i Digital a Convertidors Analògics"

- ↑ Knoll (1989, p. 664–665)

- ↑ Nicholson (1974, p. 313–315)

- ↑ Knoll (1989, p. 664–665)

- ↑ . Nicholson (1974, p. 313–315)

- ↑ Knoll (1989, p. 665–666)

- ↑ Nicholson (1974, p. 315–316)

- ↑ Knoll (1989, p. 665–666)

- ↑ . Nicholson (1974, p. 315–316)

- ↑ Atmel Application Note AVR400: Low Cost A/D Converter

- ↑ [Nota d'Aplicació de http://www.atmel.com/dyn/resources/prod_documents/doc0942.pdf Atmel Avr400: Convertidor Cost A/D Baix]

- ↑ Knoll (1989, p. 663–664)

- ↑ Nicholson (1974, p. 309–310)

- ↑ Knoll (1989, p. 663–664)

- ↑ . Nicholson (1974, p. 309–310)

- ↑ . [ww1.microchip.com/downloads/en/AppNotes/00795a.pdf Microchip AN795 "Voltage to Frequency / Frequency to Voltage Converter"] [Microtros de ww1.microchip.com/downloads/en/AppNotes/00795a.pdf An795 "Voltatge a Freqüència / Freqüència a Convertidor de Voltatge"] page 4: "13-bit A/D converter" pàgina 4: "Convertidor d'A/D de 13 mica"

- ↑ . "Elements of electronic instrumentation and measurement" [% de 22voltage-to-frequency de http://books.google.com/books?id=1yBtaaaamaaj&q= %% de 22voltage-to-frequency de 22+%22frequency+counter%22+adc&dq=%22+%22frequency+counter%22+adc "Elements d'instrumentació electrònica i mesura"] by Joseph J. Carr 1996, Page 402 per Joseph J. Carr 1996, Pàgina 402

- ↑ . "Voltage-to-Frequency Analog-to-Digital Converters" "Convertidors Analògic/Digital voltatge a Freqüència"

- ↑ . "Troubleshooting Analog Circuits" [% de 22voltage-to-frequency de%22+adc&source=bl&ots=opOmco42vk&sig=6Y8ykUt6fJab0hForhVaz2vzXpy&hl=ca&ei=bTgaSqXuL9eEngey_YiWca&sa=X&oi=book_result&ct=result&resnum=2#v=onepage&q=%de 22voltage-to-frequency de Hylqh0C&pg=Pa130&lpg=Pa130&dq=%de http://books.google.com/books?id=3kY4 22% 20adc&f=false "Depuració Circuits Analògics"] by Robert A. Pease 1991 per Robert A. Pease 1991 p. 130 p. 130

Bibliografia

[modifica]- CMOS Analog Circuit Design. ISBN 0-19-511644-5.

- The Data Conversion Handbook. Elsevier: Newnes, 2005. ISBN 0-7506-7841-0.

- Analog Integrated Circuit Design. ISBN 0-471-14448-7.

- Radiation Detection and Measurement. 2n. Nova York: John Wiley & Sons, 1989.

- Demystifying Switched-Capacitor Circuits. ISBN 0-7506-7907-7.

- Nuclear Electronics. Nova York: John Wiley & Sons, 1974.

- Delta-Sigma Data Converters. IEEE Press, 1997. ISBN 0-7803-1045-4.

- Principles of Data Conversion System Design. Nova York, Ny: IEEE Press, 1995. ISBN 0-7803-1093-4.

External links

[modifica]- Counting Type ADC A simple tutorial showing how to build your first ADC.

- An Introduction to Delta Sigma Converters A very nice overview of Delta-Sigma converter theory.

- Digital Dynamic Analysis of A/D Conversion Systems through Evaluation Software based on FFT/DFT Analysis RF Expo East, 1987

- Which ADC Architecture Is Right for Your Application? article by Walt Kester

- AN71 - The Care and Feeding of High Performance ADCs Real world circuit and layout advice

- ADC and DAC Glossary Defines commonly used technical terms.